coreboot Asrock H110 Pro BTC+

- david

- Site Admin

- Posts: 423

- Joined: Sat May 21, 2016 7:50 pm

coreboot Asrock H110 Pro BTC+

Coreboot mod by our member " walterav " make Asrock H110 Pro BTC+ almost 100% functional.In this new topic we are going to test this mod.

Join our telegram group if you wana chat or have specific questions:

https://t.me/+h2K5CX5jEZA0MWJk

Onboard I219-V LAN works on Asrock H110 Pro BTC+ !

Compiled own coreboot.rom using all defaults, but edited "devicetree.cb" to mimic older legacy pci definitions with extra disabled 1f.6 location found here look at the end of the file.

https://www.coreboot.org/fossology/?mod ... &item=9156

While the current devicetree.cb shows "ref" block definitions without mentioning location "1f.6":

https://github.com/coreboot/coreboot/bl ... icetree.cb

So I changed devicetree.cb to:

I also added the "flashdescription region3 GbE" to the coreboot rom which also used original "Descriptor and ME" regions:

PCI-E Switch ASM1187e 7-Port PCIe x1 Gen2 Packet Switch detected using these "devicetree.cb" edits:

Tested 7 different devices in all the white PCI-E asmedia switched slots at the same time, and some of the network adapters with option roms are even loaded in SeaBIOS and shows numbered PXE boot options besides the SATA/USB ! The OS detects all 7 devices!

Also tested all black 6x pci-e slots with 1X length devices, but the slot called PCIE5 won't detect device, maybe because numbering of PCI devices ends with 06 with that being the ASmedia switch controller...?

IGPU

Also onboard igpu libgfxinit works in text mode in SeaBIOS by just adding "select MAINBOARD_HAS_LIBGFXINIT" to Kconfig file from the onboard DVI connector linked to a HDMI screen. This works for both G4400 Skylake and G3950 Kabylake gpu!

Join our telegram group if you wana chat or have specific questions:

https://t.me/+h2K5CX5jEZA0MWJk

Onboard I219-V LAN works on Asrock H110 Pro BTC+ !

Compiled own coreboot.rom using all defaults, but edited "devicetree.cb" to mimic older legacy pci definitions with extra disabled 1f.6 location found here look at the end of the file.

https://www.coreboot.org/fossology/?mod ... &item=9156

Code: Select all

end # LPC Interface

device pci 1f.1 on end # P2SB

device pci 1f.2 on end # Power Management Controller

device pci 1f.3 on # Intel HDA

register "PchHdaVcType" = "Vc1"

end

device pci 1f.4 on end # SMBus

device pci 1f.5 on end # PCH SPI

device pci 1f.6 off end # GbE <--- Extra port which contains I219-V but disabled

end

endhttps://github.com/coreboot/coreboot/bl ... icetree.cb

Code: Select all

end # chip superio/common

chip drivers/pc80/tpm

device pnp 4e.0 on end # TPM module

end

end

device ref hda on

register "PchHdaVcType" = "Vc1"

end

device ref smbus on end

device ref fast_spi on end

end

endCode: Select all

end # chip superio/common

chip drivers/pc80/tpm

device pnp 4e.0 on end # TPM module

end

end

device ref hda on

register "PchHdaVcType" = "Vc1"

end

device ref smbus on end

device ref fast_spi on end

device pci 1f.6 on end # <--- enables I219-V onboard

end

endCode: Select all

ifdtool coreboot-1f6pci.rom -i Gbe:flashregion_3_gbe.binPCI-E Switch ASM1187e 7-Port PCIe x1 Gen2 Packet Switch detected using these "devicetree.cb" edits:

Code: Select all

..............................

device ref pcie_rp7 on

register "PcieRpEnable[6]" = "1"

register "PcieRpClkReqSupport[6]" = "1"

register "PcieRpClkReqNumber[6]" = "3"

register "PcieRpAdvancedErrorReporting[6]" = "1"

register "PcieRpLtrEnable[6]" = "1"

register "PcieRpClkSrcNumber[6]" = "3"

register "PcieRpHotPlug[6]" = "1"

end

### original code above ^^^

device pci 1d.0 on

register "PcieRpEnable[8]" = "1"

register "PcieRpClkReqSupport[8]" = "1"

register "PcieRpClkReqNumber[8]" = "4"

register "PcieRpAdvancedErrorReporting[8]" = "1"

register "PcieRpLtrEnable[8]" = "1"

register "PcieRpClkSrcNumber[8]" = "4"

register "PcieRpHotPlug[8]" = "1"

end

device pci 1d.1 on

register "PcieRpEnable[9]" = "1"

register "PcieRpClkReqSupport[9]" = "1"

register "PcieRpClkReqNumber[9]" = "5"

register "PcieRpAdvancedErrorReporting[9]" = "1"

register "PcieRpLtrEnable[9]" = "1"

register "PcieRpClkSrcNumber[9]" = "5"

register "PcieRpHotPlug[9]" = "1"

end

### original code below

device ref lpc_espi on

subsystemid 0x1849 0x1a43

# Set @0x280-0x2ff I/O Range for SuperIO HWM

register "gen1_dec" = "0x007c0281"

# Set LPC Serial IRQ mode

register "serirq_mode" = "SERIRQ_CONTINUOUS"

....................

lspciAlso tested all black 6x pci-e slots with 1X length devices, but the slot called PCIE5 won't detect device, maybe because numbering of PCI devices ends with 06 with that being the ASmedia switch controller...?

IGPU

Also onboard igpu libgfxinit works in text mode in SeaBIOS by just adding "select MAINBOARD_HAS_LIBGFXINIT" to Kconfig file from the onboard DVI connector linked to a HDMI screen. This works for both G4400 Skylake and G3950 Kabylake gpu!

-

walterav

- Posts: 52

- Joined: Sat Sep 07, 2024 7:08 pm

Re: coreboot Asrock H110 Pro BTC+

The built-in intel Gbe option ROM can also be included during coreboot build time, by adding the following line to "Kconfig":

select MAINBOARD_USES_IFD_GBE_REGION

From the make menuconfig chipset you can than enable the "Add gigabit ethernet configuration" and give location for the GBE.BIN file just like FD and ME BIN files extracted from the original firmware backup file(ifdtool -x). You may also remove the realtek related stuff from Kconfig since that has no purpose for the H110 Pro BTC+...

select MAINBOARD_USES_IFD_GBE_REGION

From the make menuconfig chipset you can than enable the "Add gigabit ethernet configuration" and give location for the GBE.BIN file just like FD and ME BIN files extracted from the original firmware backup file(ifdtool -x). You may also remove the realtek related stuff from Kconfig since that has no purpose for the H110 Pro BTC+...

-

walterav

- Posts: 52

- Joined: Sat Sep 07, 2024 7:08 pm

Re: coreboot Asrock H110 Pro BTC+

IGPU

The graphics initialization for the igpu using "libgfxinit" in "txt mode" and SeaBIOS is compatible with both IGPU and or PCIE 16X slot used GPU from AMD/NVIDIA at the same time. It can show SeaBIOS screen on both devices. Also the G4900T CoffeeLake iGPU works fine!

Using onboard GPU with libgfxinit in UEFI ED2K Tianocore for only the integrated GPU needs the full framebuffer mode setting instead of txt mode. This is however not compatible with PCIE 16X slot used GPU from AMD/NVIDIA. It will blackscreen on the PEG16X inserted GPU's, but after boot of OS it may function.

The graphics initialization for the igpu using "libgfxinit" in "txt mode" and SeaBIOS is compatible with both IGPU and or PCIE 16X slot used GPU from AMD/NVIDIA at the same time. It can show SeaBIOS screen on both devices. Also the G4900T CoffeeLake iGPU works fine!

Using onboard GPU with libgfxinit in UEFI ED2K Tianocore for only the integrated GPU needs the full framebuffer mode setting instead of txt mode. This is however not compatible with PCIE 16X slot used GPU from AMD/NVIDIA. It will blackscreen on the PEG16X inserted GPU's, but after boot of OS it may function.

-

walterav

- Posts: 52

- Joined: Sat Sep 07, 2024 7:08 pm

Re: coreboot Asrock H110 Pro BTC+

A WIP convert H110M-DVS into a variant (base) commit also containing code for H110 Pro BTC+ is posted:

https://review.coreboot.org/c/coreboot/+/88895

It will bring up almost the whole H110 Pro BTC+ board, except Wake On LAN see notes.

https://review.coreboot.org/c/coreboot/+/88895

It will bring up almost the whole H110 Pro BTC+ board, except Wake On LAN see notes.

- david

- Site Admin

- Posts: 423

- Joined: Sat May 21, 2016 7:50 pm

Re: coreboot Asrock H110 Pro BTC+

I found this board here localy for like 50 usd and i order it it will come in next days and i will test your new build on it.walterav wrote: ↑Fri Aug 22, 2025 10:01 am A WIP convert H110M-DVS into a variant (base) commit also containing code for H110 Pro BTC+ is posted:

https://review.coreboot.org/c/coreboot/+/88895

It will bring up almost the whole H110 Pro BTC+ board, except Wake On LAN see notes.

I`m currious cos it has so many slots can be turned into perfect mini server + router with many pci-e cards in combination with 8500 cpu

-

james2

- Posts: 30

- Joined: Sat Aug 09, 2025 6:37 am

Re: coreboot Asrock H110 Pro BTC+

I just ordered this board also, lets see how it builds.

sorry if its off topic,

You may be interested in upcoming project sovereign boot

https://docs.dasharo.com/projects/sover ... ot-wizard/

I am also trying side project; coreboot for macbook pro 11,3 based off these commit:

https://review.coreboot.org/c/coreboot/+/83900

https://review.coreboot.org/c/coreboot/+/32673

sorry if its off topic,

You may be interested in upcoming project sovereign boot

https://docs.dasharo.com/projects/sover ... ot-wizard/

I am also trying side project; coreboot for macbook pro 11,3 based off these commit:

https://review.coreboot.org/c/coreboot/+/83900

https://review.coreboot.org/c/coreboot/+/32673

-

walterav

- Posts: 52

- Joined: Sat Sep 07, 2024 7:08 pm

Re: coreboot Asrock H110 Pro BTC+

Nice to hear both of you gonna try the Asrock Pro BTC+, perhaps if I understand how the GPIO code should be addressed maybe we can split up the effort 3 way to fill in the gaps?

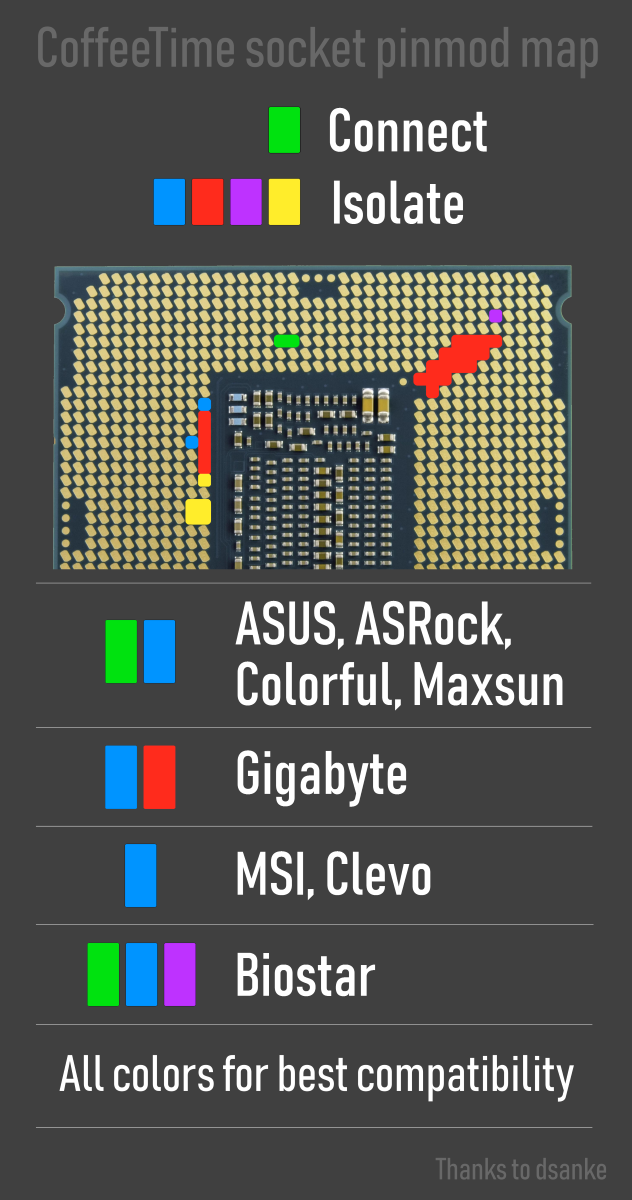

@david for the Pro BTC+ I was not successful yet in having a coffeelake i5 8500 or a coffeelake refresh i3 9100E to work. But that might be related to the physical tape/sticker pin mod or shorting trick. Can you confirm what pins you taped on the 8600 CPU?

About the macbookpro, cool project remember haswell / broadwell CPU's need "mrc.bin" system agent (extract from chromos recovery image peppy or tidus) or the new "Haswell NRI" to setup the system. Not sure NRI is compatible with mobile intel chipset... Ram is soldered onboard so you will also need to look at SPD and the macbookpro 10,x example you linked.

@david for the Pro BTC+ I was not successful yet in having a coffeelake i5 8500 or a coffeelake refresh i3 9100E to work. But that might be related to the physical tape/sticker pin mod or shorting trick. Can you confirm what pins you taped on the 8600 CPU?

About the macbookpro, cool project remember haswell / broadwell CPU's need "mrc.bin" system agent (extract from chromos recovery image peppy or tidus) or the new "Haswell NRI" to setup the system. Not sure NRI is compatible with mobile intel chipset... Ram is soldered onboard so you will also need to look at SPD and the macbookpro 10,x example you linked.

-

walterav

- Posts: 52

- Joined: Sat Sep 07, 2024 7:08 pm

Re: coreboot Asrock H110 Pro BTC+

Finally managed to get a Coffeelake 6 core (i5 8500) running in this Asrock H110 Pro BTC+ with coreboot. Although only the left side of the sticker/pin mode was done on the I5 8500 (u0), microcode was added during build it just needed the SKU to be changed in the flashdescriptor which wayward-locust on reddit reminded me to (changing 80 > A0 at position 307). The PCIe 16x slot still functions correct, tested with ethernet, wifi, sas adapter and 3.0 8x dGPU RX460 and 3.0 16x dGPU HD7700 also iGPU with dGPU works (multi-gpu)! Still using the modified corporate ME that was needed for the Xeon warm (re)boot fix.

www.reddit.com/r/coreboot/comments/1ndw ... precision/

The only thing left todo is bisect the ME cleaner stripping until the module(s) is/are found that are effective for the warm (re)boot fix and than maybe try to rebuild from a corporate ME donor without the use of the Coffeetime mod.

www.reddit.com/r/coreboot/comments/1ndw ... precision/

The only thing left todo is bisect the ME cleaner stripping until the module(s) is/are found that are effective for the warm (re)boot fix and than maybe try to rebuild from a corporate ME donor without the use of the Coffeetime mod.

- david

- Site Admin

- Posts: 423

- Joined: Sat May 21, 2016 7:50 pm

Re: coreboot Asrock H110 Pro BTC+

i did make 9600k to work on my rev3.0 board.The pinmod i used is this.What i discover is that green pin no need to be connected is still working fine like this only with this two blue isolated.

But i had to lower the TDP to 65W to be stable and i added your corporate ME that fix my problem with coldboot i did shared the rom for rev.3.0 in other topic.

- david

- Site Admin

- Posts: 423

- Joined: Sat May 21, 2016 7:50 pm

Re: coreboot Asrock H110 Pro BTC+

I got the board and 8500 cpu but i`m busy with some other work i will test them as soon i find some free time.Good finding you can upload this 8500 test rom when you think is ready for testing i will try it.walterav wrote: ↑Sat Sep 13, 2025 6:33 am Finally managed to get a Coffeelake 6 core (i5 8500) running in this Asrock H110 Pro BTC+ with coreboot. Although only the left side of the sticker/pin mode was done on the I5 8500 (u0), microcode was added during build it just needed the SKU to be changed in the flashdescriptor which wayward-locust on reddit reminded me to (changing 80 > A0 at position 307). The PCIe 16x slot still functions correct, tested with ethernet, wifi, sas adapter and 3.0 8x dGPU RX460 and 3.0 16x dGPU HD7700 also iGPU with dGPU works (multi-gpu)! Still using the modified corporate ME that was needed for the Xeon warm (re)boot fix.

www.reddit.com/r/coreboot/comments/1ndw ... precision/

The only thing left todo is bisect the ME cleaner stripping until the module(s) is/are found that are effective for the warm (re)boot fix and than maybe try to rebuild from a corporate ME donor without the use of the Coffeetime mod.