coreboot on ASRock H110M-DVS rev 3.0 and rev 2.0 and me_cleaner

-

james

- Posts: 2

- Joined: Sun Aug 03, 2025 12:16 am

Re: coreboot on ASRock H110M-DVS rev 3.0 and rev 2.0 and me_cleaner

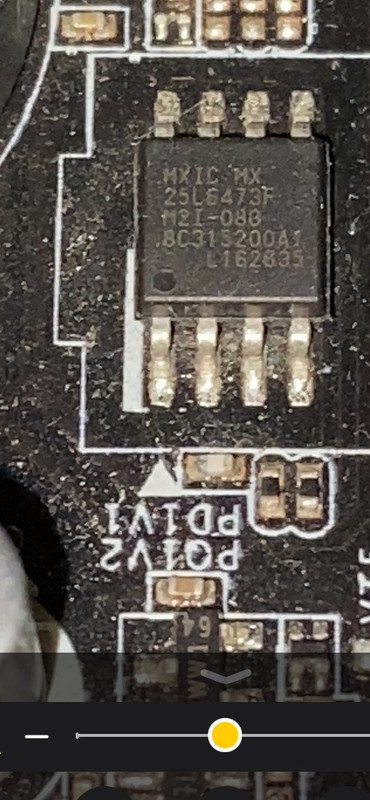

James here, I made an accountdavid wrote: ↑Sat Aug 02, 2025 1:09 pmCan you post pictures here to see them ? I still have rev 3.0 in august i will try to continue testing it.jameswoody wrote: ↑Sat Aug 02, 2025 11:46 am My chip on the rev 3.0 looks to be a MX25L6473 F (it doesn't look like an E)

and not your "W25Q64JV-.Q"

-

james

- Posts: 2

- Joined: Sun Aug 03, 2025 12:16 am

Re: coreboot on ASRock H110M-DVS rev 3.0 and rev 2.0 and me_cleaner

I couldnt really find a list of differences between rev3.0 and 2.0 but copilot said.

https://copilot.microsoft.com/chats/gxC ... SdKjE5EAoA

Power Design

R2.0: 5-phase Digi Power design, supports CPUs up to 91W

R3.0: 4-phase power design, supports CPUs up to 95W

how far did you get with the 2.0 rom?

btw I will be using an i7-7700k

https://copilot.microsoft.com/chats/gxC ... SdKjE5EAoA

Power Design

R2.0: 5-phase Digi Power design, supports CPUs up to 91W

R3.0: 4-phase power design, supports CPUs up to 95W

how far did you get with the 2.0 rom?

btw I will be using an i7-7700k

-

walterav

- Posts: 52

- Joined: Sat Sep 07, 2024 7:08 pm

Re: coreboot on ASRock H110M-DVS rev 3.0 and rev 2.0 and me_cleaner

Hi all, will not thread hijack again this time  , but if my Dell Optiplex 3050 variant is accepted in coreboot upstream I will try to convert the "Asrock H110M" code into a variant supporting both the Asrock H110M REV2 and the Asrock H110 Pro BTC+ and maybe the REV 3 you guys have?

, but if my Dell Optiplex 3050 variant is accepted in coreboot upstream I will try to convert the "Asrock H110M" code into a variant supporting both the Asrock H110M REV2 and the Asrock H110 Pro BTC+ and maybe the REV 3 you guys have?

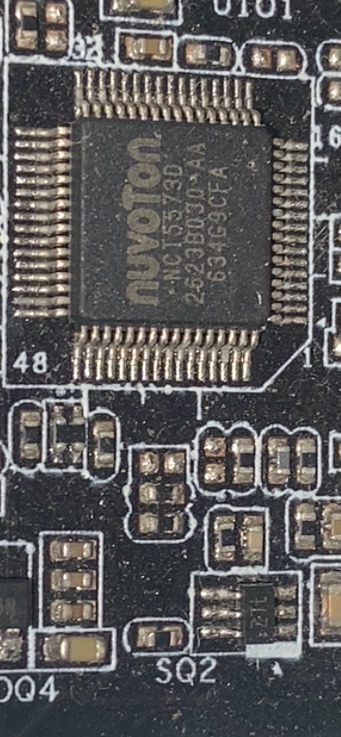

A quick photo comparison of the difference between the REV2 and REV3 seems to be that the "superio chip" changed, on the REV 2 it a "nuvoton" NCT6791D but the REV 3 looks smaller but still seems nuvoton?

@James can you tell me which superio chip brand / type is on the REV3 motherboard, can you also post some `sudo sensor-detect #lm-sensors` code to see at what address it is?

If you found the superio model you can for instance try to find its code in the coreboot codebase to look for examples how it is used to initiate the SP1 serial port / uart, since coreboot RAM init debugging blind is kinda hard:

If you want to debug blind, remove superio code that is not for your specific model than look at RAM slot initiation first see `romstage.c` eliminate one whole slot { 0x50, 0x52 }, as in { 0x50} or only { 0x52 }, or even only { 0x53 }, or { 0x51} if you cannot try a single slot use 0 for the second place and swap them around. {0x50, 0} or {0, 0x50}. Or fake 4 slots to give yourself the chance to find correct slot {0x50,0,0,0} {0,0,0,50} {0,50,0,0} {0,0,50,0} so on for 53 52 51 If one works at certain position try next value at other positions. If you not lucky you maye find in around 16 positions something that works

Probably also remove corresponding lines if you test only one position or multiply them to 4 'mem_cfg->MemorySpdPtr10 = (uintptr_t)blk.spd_array[1];' play with ptr 01 / 10 / 00 11 and array[0/1/2/3].

For hints?

https://ticket.coreboot.org/issues/594

A quick photo comparison of the difference between the REV2 and REV3 seems to be that the "superio chip" changed, on the REV 2 it a "nuvoton" NCT6791D but the REV 3 looks smaller but still seems nuvoton?

@James can you tell me which superio chip brand / type is on the REV3 motherboard, can you also post some `sudo sensor-detect #lm-sensors` code to see at what address it is?

If you found the superio model you can for instance try to find its code in the coreboot codebase to look for examples how it is used to initiate the SP1 serial port / uart, since coreboot RAM init debugging blind is kinda hard:

Code: Select all

egrep -r NCT6791D . | grep mainboard

./src/mainboard/asrock/h110m/bootblock.c: const pnp_devfn_t serial_dev = PNP_DEV(0x2e, NCT6791D_SP1);

./src/mainboard/asrock/h110m/Kconfig: select SUPERIO_NUVOTON_NCT6791D

./src/mainboard/asrock/z97_extreme6/bootblock.c:#define SERIAL_DEV PNP_DEV(0x2e, NCT6791D_SP1)

./src/mainboard/asrock/z97_extreme6/bootblock.c:#define ACPI_DEV PNP_DEV(0x2e, NCT6791D_ACPI)

./src/mainboard/asrock/z97_extreme6/bootblock.c:#define GPIO_PP_OD_DEV PNP_DEV(0x2e, NCT6791D_GPIO_PP_OD)

./src/mainboard/asrock/z97_extreme6/Kconfig: select SUPERIO_NUVOTON_NCT6791D

./src/mainboard/purism/librem_l1um_v2/bootblock.c: * Disable the Nuvoton NCT6791D SuperIO UART1. It is enabled by

./src/mainboard/purism/librem_l1um_v2/bootblock.c: const pnp_devfn_t nvt_serial_dev = PNP_DEV(0x2E, NCT6791D_SP1);

./src/mainboard/purism/librem_l1um_v2/Kconfig: select SUPERIO_NUVOTON_NCT6791D # This board has two SuperIOs

./Documentation/mainboard/asrock/h110m-dvs.md:- NCT6791D GPIOs

./Documentation/mainboard/asrock/h110m-dvs.md:| Super I/O | Nuvoton NCT6791D

Probably also remove corresponding lines if you test only one position or multiply them to 4 'mem_cfg->MemorySpdPtr10 = (uintptr_t)blk.spd_array[1];' play with ptr 01 / 10 / 00 11 and array[0/1/2/3].

For hints?

https://ticket.coreboot.org/issues/594

Last edited by walterav on Sat Aug 09, 2025 7:58 am, edited 2 times in total.

-

james2

- Posts: 30

- Joined: Sat Aug 09, 2025 6:37 am

Re: coreboot on ASRock H110M-DVS rev 3.0 and rev 2.0 and me_cleaner

Last edited by james2 on Sat Aug 09, 2025 7:01 am, edited 1 time in total.

-

james2

- Posts: 30

- Joined: Sat Aug 09, 2025 6:37 am

Re: coreboot on ASRock H110M-DVS rev 3.0 and rev 2.0 and me_cleaner

its a nuvoton NCT5573D.

As far as I can tell there is no mention of that in coreboot.

I am thinking this could be the right entry on devicetree.cb:

also adding updating

src/superio/nuvoton/nuvoton.c

Is this the same chip on yours @david?

edit.. after some searching I found a datasheet

https://www.censtry.com/product/nuvoton/nct5573d.html

As far as I can tell there is no mention of that in coreboot.

I am thinking this could be the right entry on devicetree.cb:

Code: Select all

chip superio/nuvoton/nct5573d

device pnp 2e.2 on # UART COM1

io 0x60 = 0x3F8

irq 0x70 = 4

end

device pnp 2e.f on # GPIO

# Example GPIO configuration here

end

end

src/superio/nuvoton/nuvoton.c

Is this the same chip on yours @david?

edit.. after some searching I found a datasheet

https://www.censtry.com/product/nuvoton/nct5573d.html

-

walterav

- Posts: 52

- Joined: Sat Sep 07, 2024 7:08 pm

Re: coreboot on ASRock H110M-DVS rev 3.0 and rev 2.0 and me_cleaner

There are currently 2 other nct55xx supported, but the 5572d comes numerical closer

https://github.com/coreboot/coreboot/tr ... o/nuvoton/

Try to compare your datasheet uart/com/sp1 pinout to the one in datasheet 5572d (google) if it looks similar you may use the code of nct5572d.

There is also a pull request for a 5535d:

https://review.coreboot.org/c/coreboot/+/85834

Please provide lm-sensors, sensors-detect output if one Linux distro fails try a newer one I use both KDE NEON and Fedora42. Do you see motherboard HWM sensors in lm-sensors as in fanspeed voltages? Your try running `sudo modeprobe nct6775` and check lm-sensors again?

If you found something that reminds of a adress of superio see this ticket and read 5 last comments, it will help you detect / hint what the adresses are and than adjust the coreboot/util/superiotool/nuvoton.c code to match/replace your chip 0xb473 if needed!

https://ticket.coreboot.org/issues/455

Than do a real good dump with the superio tool, I do had to skip/block the AASPEED and infineon brands detects because it messes up the nuvoton detection, you may only have one try each boot because wrong probing locks up the superio, so you won't detect it anymore.

If you get a good superio.log than you can fill the details in devicetree.cb with correct addresses, but you will also have to adjust Kconfig with correct superio, than don't forget to do "make menuconfig" again after that otherwise the changes in Kconfig will not be taken into account next build.

https://github.com/coreboot/coreboot/tr ... o/nuvoton/

Try to compare your datasheet uart/com/sp1 pinout to the one in datasheet 5572d (google) if it looks similar you may use the code of nct5572d.

There is also a pull request for a 5535d:

https://review.coreboot.org/c/coreboot/+/85834

Please provide lm-sensors, sensors-detect output if one Linux distro fails try a newer one I use both KDE NEON and Fedora42. Do you see motherboard HWM sensors in lm-sensors as in fanspeed voltages? Your try running `sudo modeprobe nct6775` and check lm-sensors again?

If you found something that reminds of a adress of superio see this ticket and read 5 last comments, it will help you detect / hint what the adresses are and than adjust the coreboot/util/superiotool/nuvoton.c code to match/replace your chip 0xb473 if needed!

https://ticket.coreboot.org/issues/455

Than do a real good dump with the superio tool, I do had to skip/block the AASPEED and infineon brands detects because it messes up the nuvoton detection, you may only have one try each boot because wrong probing locks up the superio, so you won't detect it anymore.

If you get a good superio.log than you can fill the details in devicetree.cb with correct addresses, but you will also have to adjust Kconfig with correct superio, than don't forget to do "make menuconfig" again after that otherwise the changes in Kconfig will not be taken into account next build.

Last edited by walterav on Sat Aug 09, 2025 8:02 am, edited 1 time in total.

-

walterav

- Posts: 52

- Joined: Sat Sep 07, 2024 7:08 pm

Re: coreboot on ASRock H110M-DVS rev 3.0 and rev 2.0 and me_cleaner

Code: Select all

egrep -r NCT557 . | grep mainboard

./src/mainboard/intel/dcp847ske/early_southbridge.c: * Since the NCT5577D fan control only supports positive values,

./src/mainboard/intel/dcp847ske/Kconfig: NCT5577D pin 18 (txd) and gnd.

Code: Select all

sudo superiotool -l | grep 557

Nuvoton NCT6775F (B) / NCT5572D (B) (not all LDNs supported) (dump available)

Would edit your chip_id=xxxx into https://github.com/coreboot/coreboot/bl ... /nuvoton.c #0xb473 and try superiotool dump that way. But first find the correct address and chip id!

- david

- Site Admin

- Posts: 422

- Joined: Sat May 21, 2016 7:50 pm

Re: coreboot on ASRock H110M-DVS rev 3.0 and rev 2.0 and me_cleaner

Welcome back walterav! Recently i got 9600k and tested it on rev 3.0 with modified microcodes updates on Original bios and me disabled it works but only on cold boot mean i need to power off and power on from atx power supply strange behavior but i remeber you had somthing similar with your Xeon so just decided to post it, i still keep my old cpu for testing with porting coreboot to rev 3.0 so i will check your information you provided guys! Also will get 8500 for testing too.walterav wrote: ↑Fri Aug 08, 2025 9:30 pm Hi all, will not thread hijack again this time, but if my Dell Optiplex 3050 variant is accepted in coreboot upstream I will try to convert the "Asrock H110M" code into a variant supporting both the Asrock H110M REV2 and the Asrock H110 Pro BTC+ and maybe the REV 3 you guys have?

A quick photo comparison of the difference between the REV2 and REV3 seems to be that the "superio chip" changed, on the REV 2 it a "nuvoton" NCT6791D but the REV 3 looks smaller but still seems nuvoton?

@James can you tell me which superio chip brand / type is on the REV3 motherboard, can you also post some `sudo sensor-detect #lm-sensors` code to see at what address it is?

If you found the superio model you can for instance try to find its code in the coreboot codebase to look for examples how it is used to initiate the SP1 serial port / uart, since coreboot RAM init debugging blind is kinda hard:If you want to debug blind, remove superio code that is not for your specific model than look at RAM slot initiation first see `romstage.c` eliminate one whole slot { 0x50, 0x52 }, as in { 0x50} or only { 0x52 }, or even only { 0x53 }, or { 0x51} if you cannot try a single slot use 0 for the second place and swap them around. {0x50, 0} or {0, 0x50}. Or fake 4 slots to give yourself the chance to find correct slot {0x50,0,0,0} {0,0,0,50} {0,50,0,0} {0,0,50,0} so on for 53 52 51 If one works at certain position try next value at other positions. If you not lucky you maye find in around 16 positions something that worksCode: Select all

egrep -r NCT6791D . | grep mainboard ./src/mainboard/asrock/h110m/bootblock.c: const pnp_devfn_t serial_dev = PNP_DEV(0x2e, NCT6791D_SP1); ./src/mainboard/asrock/h110m/Kconfig: select SUPERIO_NUVOTON_NCT6791D ./src/mainboard/asrock/z97_extreme6/bootblock.c:#define SERIAL_DEV PNP_DEV(0x2e, NCT6791D_SP1) ./src/mainboard/asrock/z97_extreme6/bootblock.c:#define ACPI_DEV PNP_DEV(0x2e, NCT6791D_ACPI) ./src/mainboard/asrock/z97_extreme6/bootblock.c:#define GPIO_PP_OD_DEV PNP_DEV(0x2e, NCT6791D_GPIO_PP_OD) ./src/mainboard/asrock/z97_extreme6/Kconfig: select SUPERIO_NUVOTON_NCT6791D ./src/mainboard/purism/librem_l1um_v2/bootblock.c: * Disable the Nuvoton NCT6791D SuperIO UART1. It is enabled by ./src/mainboard/purism/librem_l1um_v2/bootblock.c: const pnp_devfn_t nvt_serial_dev = PNP_DEV(0x2E, NCT6791D_SP1); ./src/mainboard/purism/librem_l1um_v2/Kconfig: select SUPERIO_NUVOTON_NCT6791D # This board has two SuperIOs ./Documentation/mainboard/asrock/h110m-dvs.md:- NCT6791D GPIOs ./Documentation/mainboard/asrock/h110m-dvs.md:| Super I/O | Nuvoton NCT6791D

Probably also remove corresponding lines if you test only one position or multiply them to 4 'mem_cfg->MemorySpdPtr10 = (uintptr_t)blk.spd_array[1];' play with ptr 01 / 10 / 00 11 and array[0/1/2/3].

For hints?

https://ticket.coreboot.org/issues/594

-

james2

- Posts: 30

- Joined: Sat Aug 09, 2025 6:37 am

Re: coreboot on ASRock H110M-DVS rev 3.0 and rev 2.0 and me_cleaner

Hi guys,

so the superio dump was succesful.

superiotool r25.06-340-g8f09629fb1

Found Nuvoton NCT6776F/D (C) (id=0xc333) at 0x2e

Register dump:

idx 10 11 13 14 16 17 18 19 1a 1b 1c 1d 1e 1f 20 21 22 23 24 25 26 27 28 2a 2b 2c 2d 2e 2f

val ff ff ff ff ff ff ff ff b8 6e 00 00 ff ff c3 33 ff 00 78 00 00 00 00 c0 00 80 00 00 00

def ff ff 00 00 ff ff ff ff f0 78 00 00 ff ff c3 33 ff 00 64 00 MM 00 00 c0 00 81 00 00 MM

LDN 0x00 (FDC)

idx 30 60 61 70 74 f0 f1 f2 f4 f5

val 00 03 f0 06 02 0e 00 ff 00 00

def 01 03 f0 06 02 0e 00 ff 00 00

LDN 0x01 (Parallel Port)

idx 30 60 61 70 74 f0

val 00 03 78 07 04 3f

def 01 03 78 07 04 3f

LDN 0x02 (UART A)

idx 30 60 61 70 f0 f2

val 00 03 f8 04 00 00

def 01 03 f8 04 00 00

LDN 0x03 (UART B, IR)

idx 30 60 61 70 f0 f1 f2

val 00 02 f8 03 00 00 00

def 01 02 f8 03 00 00 00

LDN 0x05 (Keyboard Controller)

idx 30 60 61 62 63 70 72 f0

val 01 00 60 00 64 01 0c 83

def 00 00 00 00 00 00 00 83

LDN 0x06 (CIR)

idx 30 60 61 70 f0 f1 f2 f3

val 00 00 00 00 08 09 32 00

def 00 00 00 00 08 09 32 00

LDN 0x07 (GPIO6, GPIO7, GPIO8, GPIO9)

idx 30 e0 e1 e2 e3 e4 e5 e6 e7 e8 e9 ea eb ec ed ee f4 f5 f6 f7 f8

val 00 ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff

def 03 ff 00 00 00 ef 00 00 00 ff 00 00 00 00 00 00 ff 00 00 00 00

LDN 0x08 (WDT1, GPIO0, GPIO1, GPIOA)

idx 30 60 61 e0 e1 e2 e3 e4 f0 f1 f2 f3 f4 f5 f6 f7

val 04 00 00 ff ff ff ff ff ff ff ff ff ff ff 00 ff

def 02 00 00 ff 00 00 00 00 ff 00 00 00 00 00 00 00

LDN 0x09 (GPIO2, GPIO3, GPIO4, GPIO5)

idx 30 e0 e1 e2 e3 e4 e5 e6 e7 e8 e9 ea eb ee f0 f1 f2 f4 f5 f6 f7 fe

val 14 cf 20 00 00 ff ff ff ff 02 00 ff ff 00 bf 00 00 ff ff ff ff 00

def 04 df 00 00 00 ff 00 00 00 00 00 00 00 00 ff 00 00 ff 00 00 00 00

LDN 0x0a (ACPI)

idx e0 e1 e2 e3 e4 e5 e6 e7 e9 ee f0 f2 f3 f4 f6 f7 fe

val 01 00 00 00 00 00 48 00 10 00 20 dc 00 00 00 c0 00

def 01 00 00 00 00 02 1c 00 00 00 00 5c 00 00 00 c0 00

LDN 0x0b (Hardware Monitor, Front Panel LED)

idx 30 60 61 62 63 70 e0 e1 e2 f0 f1 f2 f5 f6 f7 f8 f9 fa

val 01 02 90 02 a0 00 7f 7f ff 00 00 00 10 00 87 27 00 00

def 00 00 00 00 00 00 7f 7f ff 00 00 00 10 00 87 47 00 00

LDN 0x0d (VID)

idx e0 e1 e2 e3 e4 e5 e6 e9 ee ef f0 f4 f5

val 00 00 ff ff 00 00 00 00 88 00 00 00 00

def 00 00 00 00 00 00 00 00 88 00 00 00 00

LDN 0x0e (CIR WAKE-UP)

idx 30 60 61 70

val 00 00 00 00

def 00 00 00 00

LDN 0x0f (GPIO Push-Pull or Open-drain)

idx e0 e1 e2 e3 e4 e5 e6 e7 e8 e9 f0 f1 f2

val ff df ff fe f6 ff ff d3 ff 9f 00 00 00

def ff df ff fe f6 ff ff d3 ff 9f 00 00 00

LDN 0x14 (SVID)

idx e0 e1 e3 e4

val 00 80 00 00

def 00 80 00 00

LDN 0x16 (Deep Sleep)

idx 30 e0 e1 e2

val 20 20 04 05

def 20 20 04 05

LDN 0x17 (GPIOA)

idx e0 e1 e2 e3 e4 e5

val 01 00 00 00 01 00

def 01 00 00 00 01 00

IM-Sensors:

Trying family `VIA/Winbond/Nuvoton/Fintek'... Yes

Found `Nuvoton NCT5573D/NCT5577D/NCT6776F Super IO Sensors' Success!

(address 0x290, driver `nct6775')

Probing for Super-I/O at 0x4e/0x4f

so

ID = 0xC333 confirms this is NCT5573D (shared ID with NCT6776F).

Detected at 0x2E config port, so no need to switch to 0x4E.

Kernel driver (nct6775) already recognizes this chip for HWM.

so

src/superio/nuvoton/nct5572d/nct5572d.c

Many thanks again to you both...

so the superio dump was succesful.

superiotool r25.06-340-g8f09629fb1

Found Nuvoton NCT6776F/D (C) (id=0xc333) at 0x2e

Register dump:

idx 10 11 13 14 16 17 18 19 1a 1b 1c 1d 1e 1f 20 21 22 23 24 25 26 27 28 2a 2b 2c 2d 2e 2f

val ff ff ff ff ff ff ff ff b8 6e 00 00 ff ff c3 33 ff 00 78 00 00 00 00 c0 00 80 00 00 00

def ff ff 00 00 ff ff ff ff f0 78 00 00 ff ff c3 33 ff 00 64 00 MM 00 00 c0 00 81 00 00 MM

LDN 0x00 (FDC)

idx 30 60 61 70 74 f0 f1 f2 f4 f5

val 00 03 f0 06 02 0e 00 ff 00 00

def 01 03 f0 06 02 0e 00 ff 00 00

LDN 0x01 (Parallel Port)

idx 30 60 61 70 74 f0

val 00 03 78 07 04 3f

def 01 03 78 07 04 3f

LDN 0x02 (UART A)

idx 30 60 61 70 f0 f2

val 00 03 f8 04 00 00

def 01 03 f8 04 00 00

LDN 0x03 (UART B, IR)

idx 30 60 61 70 f0 f1 f2

val 00 02 f8 03 00 00 00

def 01 02 f8 03 00 00 00

LDN 0x05 (Keyboard Controller)

idx 30 60 61 62 63 70 72 f0

val 01 00 60 00 64 01 0c 83

def 00 00 00 00 00 00 00 83

LDN 0x06 (CIR)

idx 30 60 61 70 f0 f1 f2 f3

val 00 00 00 00 08 09 32 00

def 00 00 00 00 08 09 32 00

LDN 0x07 (GPIO6, GPIO7, GPIO8, GPIO9)

idx 30 e0 e1 e2 e3 e4 e5 e6 e7 e8 e9 ea eb ec ed ee f4 f5 f6 f7 f8

val 00 ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff

def 03 ff 00 00 00 ef 00 00 00 ff 00 00 00 00 00 00 ff 00 00 00 00

LDN 0x08 (WDT1, GPIO0, GPIO1, GPIOA)

idx 30 60 61 e0 e1 e2 e3 e4 f0 f1 f2 f3 f4 f5 f6 f7

val 04 00 00 ff ff ff ff ff ff ff ff ff ff ff 00 ff

def 02 00 00 ff 00 00 00 00 ff 00 00 00 00 00 00 00

LDN 0x09 (GPIO2, GPIO3, GPIO4, GPIO5)

idx 30 e0 e1 e2 e3 e4 e5 e6 e7 e8 e9 ea eb ee f0 f1 f2 f4 f5 f6 f7 fe

val 14 cf 20 00 00 ff ff ff ff 02 00 ff ff 00 bf 00 00 ff ff ff ff 00

def 04 df 00 00 00 ff 00 00 00 00 00 00 00 00 ff 00 00 ff 00 00 00 00

LDN 0x0a (ACPI)

idx e0 e1 e2 e3 e4 e5 e6 e7 e9 ee f0 f2 f3 f4 f6 f7 fe

val 01 00 00 00 00 00 48 00 10 00 20 dc 00 00 00 c0 00

def 01 00 00 00 00 02 1c 00 00 00 00 5c 00 00 00 c0 00

LDN 0x0b (Hardware Monitor, Front Panel LED)

idx 30 60 61 62 63 70 e0 e1 e2 f0 f1 f2 f5 f6 f7 f8 f9 fa

val 01 02 90 02 a0 00 7f 7f ff 00 00 00 10 00 87 27 00 00

def 00 00 00 00 00 00 7f 7f ff 00 00 00 10 00 87 47 00 00

LDN 0x0d (VID)

idx e0 e1 e2 e3 e4 e5 e6 e9 ee ef f0 f4 f5

val 00 00 ff ff 00 00 00 00 88 00 00 00 00

def 00 00 00 00 00 00 00 00 88 00 00 00 00

LDN 0x0e (CIR WAKE-UP)

idx 30 60 61 70

val 00 00 00 00

def 00 00 00 00

LDN 0x0f (GPIO Push-Pull or Open-drain)

idx e0 e1 e2 e3 e4 e5 e6 e7 e8 e9 f0 f1 f2

val ff df ff fe f6 ff ff d3 ff 9f 00 00 00

def ff df ff fe f6 ff ff d3 ff 9f 00 00 00

LDN 0x14 (SVID)

idx e0 e1 e3 e4

val 00 80 00 00

def 00 80 00 00

LDN 0x16 (Deep Sleep)

idx 30 e0 e1 e2

val 20 20 04 05

def 20 20 04 05

LDN 0x17 (GPIOA)

idx e0 e1 e2 e3 e4 e5

val 01 00 00 00 01 00

def 01 00 00 00 01 00

IM-Sensors:

Trying family `VIA/Winbond/Nuvoton/Fintek'... Yes

Found `Nuvoton NCT5573D/NCT5577D/NCT6776F Super IO Sensors' Success!

(address 0x290, driver `nct6775')

Probing for Super-I/O at 0x4e/0x4f

so

ID = 0xC333 confirms this is NCT5573D (shared ID with NCT6776F).

Detected at 0x2E config port, so no need to switch to 0x4E.

Kernel driver (nct6775) already recognizes this chip for HWM.

so

src/superio/nuvoton/nct5572d/nct5572d.c

Code: Select all

static const struct superio_id nuvoton_ids[] = {

{ 0xc333, "NCT5573D" },

...

};

-

walterav

- Posts: 52

- Joined: Sat Sep 07, 2024 7:08 pm

Re: coreboot on ASRock H110M-DVS rev 3.0 and rev 2.0 and me_cleaner

Nice, only if you have the skill edit / add extra src/superio/nuvoton/nctXXXX code I don't. I'd rather reuse the existing NCT6776 code which 0xc333 triggered.

There are countless board examples to chose from, already more the 10 Asrock boards using NCT6776 just pick the first Z97e-itx_ac?.

Just copy the `Kconfig` settings related to NCT6776 , edit also `bootblock.c` to include the superio acpi/sp1 setup block matching the donor board and edit `devicetree.cb` to match the nct6776 correct name and adres 2e.2 using valid uart sp1 settings?

PS: again don't forget to rerun "make menuconfig" it will ask you to save changes although you haven't altered anything in the menu you probably did in Kconfig NCTxxxx code after last build otherwise you keep getting errors...

There are countless board examples to chose from, already more the 10 Asrock boards using NCT6776 just pick the first Z97e-itx_ac?.

Code: Select all

egrep -r NCT6776 | grep main

src/mainboard/asrock/z97e-itx_ac/bootblock.c:#define SERIAL_DEV PNP_DEV(0x2e, NCT6776_SP1)

src/mainboard/asrock/z97e-itx_ac/Kconfig: select SUPERIO_NUVOTON_NCT6776

src/mainboard/asrock/z87m_extreme4/bootblock.c:#define SERIAL_DEV PNP_DEV(0x2e, NCT6776_SP1)

src/mainboard/asrock/z87m_extreme4/bootblock.c:#define ACPI_DEV PNP_DEV(0x2e, NCT6776_ACPI)

src/mainboard/asrock/z87m_extreme4/Kconfig: select SUPERIO_NUVOTON_NCT6776

src/mainboard/asrock/fatal1ty_z87_professional/smihandler.c:#define GPIO1_DEV PNP_DEV(0x2e, NCT6776_WDT1_GPIO01A_V)

src/mainboard/asrock/fatal1ty_z87_professional/mainboard.c:#define GPIO1_DEV PNP_DEV(0x2e, NCT6776_WDT1_GPIO01A_V)

src/mainboard/asrock/fatal1ty_z87_professional/bootblock.c:#define GPIO1_DEV PNP_DEV(0x2e, NCT6776_WDT1_GPIO01A_V)

src/mainboard/asrock/fatal1ty_z87_professional/bootblock.c:#define GPIO1_ENABLE_DEV PNP_DEV(0x2e, NCT6776_GPIO1234567_V)

src/mainboard/asrock/fatal1ty_z87_professional/bootblock.c:#define SERIAL_DEV PNP_DEV(0x2e, NCT6776_SP1)

src/mainboard/asrock/fatal1ty_z87_professional/bootblock.c:#define ACPI_DEV PNP_DEV(0x2e, NCT6776_ACPI)

src/mainboard/asrock/fatal1ty_z87_professional/Kconfig: select SUPERIO_NUVOTON_NCT6776

src/mainboard/asrock/b85m_pro4/bootblock.c:#define SERIAL_DEV PNP_DEV(0x2e, NCT6776_SP1)

src/mainboard/asrock/b85m_pro4/bootblock.c:#define ACPI_DEV PNP_DEV(0x2e, NCT6776_ACPI)

src/mainboard/asrock/b85m_pro4/Kconfig: select SUPERIO_NUVOTON_NCT6776

src/mainboard/asrock/h81m-hds/acpi/superio.asl:#define NCT6776_SHOW_PP

src/mainboard/asrock/h81m-hds/acpi/superio.asl:#define NCT6776_SHOW_SP1

src/mainboard/asrock/h81m-hds/acpi/superio.asl:#define NCT6776_SHOW_KBC

src/mainboard/asrock/h81m-hds/acpi/superio.asl:#define NCT6776_SHOW_HWM

src/mainboard/asrock/h81m-hds/acpi/superio.asl:#undef NCT6776_SHOW_GPIO

src/mainboard/asrock/h81m-hds/bootblock.c: const pnp_devfn_t SERIAL_DEV = PNP_DEV(0x2e, NCT6776_SP1);

src/mainboard/asrock/h81m-hds/bootblock.c: const pnp_devfn_t ACPI_DEV = PNP_DEV(0x2e, NCT6776_ACPI);

src/mainboard/asrock/h81m-hds/bootblock.c: const pnp_devfn_t IR_DEV = PNP_DEV(0x2e, NCT6776_SP2);

src/mainboard/asrock/h81m-hds/Kconfig: select SUPERIO_NUVOTON_NCT6776

src/mainboard/asrock/z87_extreme4/smihandler.c:#define GPIO1_DEV PNP_DEV(0x2e, NCT6776_WDT1_GPIO01A_V)

src/mainboard/asrock/z87_extreme4/mainboard.c:#define GPIO1_DEV PNP_DEV(0x2e, NCT6776_WDT1_GPIO01A_V)

src/mainboard/asrock/z87_extreme4/bootblock.c:#define GPIO1_DEV PNP_DEV(0x2e, NCT6776_WDT1_GPIO01A_V)

src/mainboard/asrock/z87_extreme4/bootblock.c:#define GPIO1_ENABLE_DEV PNP_DEV(0x2e, NCT6776_GPIO1234567_V)

src/mainboard/asrock/z87_extreme4/bootblock.c:#define SERIAL_DEV PNP_DEV(0x2e, NCT6776_SP1)

src/mainboard/asrock/z87_extreme4/bootblock.c:#define ACPI_DEV PNP_DEV(0x2e, NCT6776_ACPI)

src/mainboard/asrock/z87_extreme4/Kconfig: select SUPERIO_NUVOTON_NCT6776

src/mainboard/asrock/z87e-itx/bootblock.c: const pnp_devfn_t SERIAL_DEV = PNP_DEV(0x2e, NCT6776_SP1);

src/mainboard/asrock/z87e-itx/bootblock.c: const pnp_devfn_t ACPI_DEV = PNP_DEV(0x2e, NCT6776_ACPI);

src/mainboard/asrock/z87e-itx/Kconfig: select SUPERIO_NUVOTON_NCT6776

src/mainboard/asrock/z87_pro4/bootblock.c:#define SERIAL_DEV PNP_DEV(0x2e, NCT6776_SP1)

src/mainboard/asrock/z87_pro4/bootblock.c:#define ACPI_DEV PNP_DEV(0x2e, NCT6776_ACPI)

src/mainboard/asrock/z87_pro4/Kconfig: select SUPERIO_NUVOTON_NCT6776

src/mainboard/asrock/h77pro4-m/early_init.c:#define SERIAL_DEV PNP_DEV(0x2e, NCT6776_SP1)

src/mainboard/asrock/h77pro4-m/early_init.c:#define GPIO6789_DEV PNP_DEV(0x2e, NCT6776_GPIO6789_V)

src/mainboard/asrock/h77pro4-m/Kconfig: select SUPERIO_NUVOTON_NCT6776

src/mainboard/asrock/b75m-itx/Kconfig: select SUPERIO_NUVOTON_NCT6776

src/mainboard/asrock/b75pro3-m/acpi/superio.asl:#define NCT6776_SHOW_SP1 1

src/mainboard/asrock/b75pro3-m/acpi/superio.asl:#define NCT6776_SHOW_KBC 1

src/mainboard/asrock/b75pro3-m/early_init.c:#define SERIAL_DEV PNP_DEV(0x2e, NCT6776_SP1)

src/mainboard/asrock/b75pro3-m/Kconfig: select SUPERIO_NUVOTON_NCT6776

src/mainboard/asrock/z87_extreme3/bootblock.c:#define SERIAL_DEV PNP_DEV(0x2e, NCT6776_SP1)

src/mainboard/asrock/z87_extreme3/bootblock.c:#define ACPI_DEV PNP_DEV(0x2e, NCT6776_ACPI)

src/mainboard/asrock/z87_extreme3/Kconfig: select SUPERIO_NUVOTON_NCT6776

src/mainboard/asrock/z87m_oc_formula/Kconfig: select SUPERIO_NUVOTON_NCT6776

src/mainboard/asrock/g41c-gs/early_init.c:#define SERIAL_DEV_R2 PNP_DEV(0x2e, NCT6776_SP1)

src/mainboard/asrock/g41c-gs/early_init.c: if (CONFIG(SUPERIO_NUVOTON_NCT6776)) {

src/mainboard/asrock/g41c-gs/Kconfig: select SUPERIO_NUVOTON_NCT6776 if BOARD_ASROCK_G41C_GS_R2_0

PS: again don't forget to rerun "make menuconfig" it will ask you to save changes although you haven't altered anything in the menu you probably did in Kconfig NCTxxxx code after last build otherwise you keep getting errors...