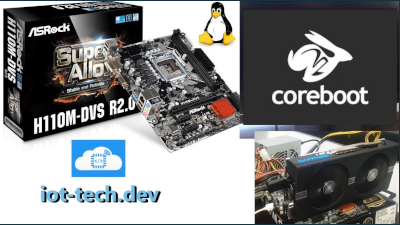

coreboot on ASRock H110M-DVS rev 3.0 and rev 2.0 and me_cleaner

Posted: Thu Aug 15, 2024 12:07 pm

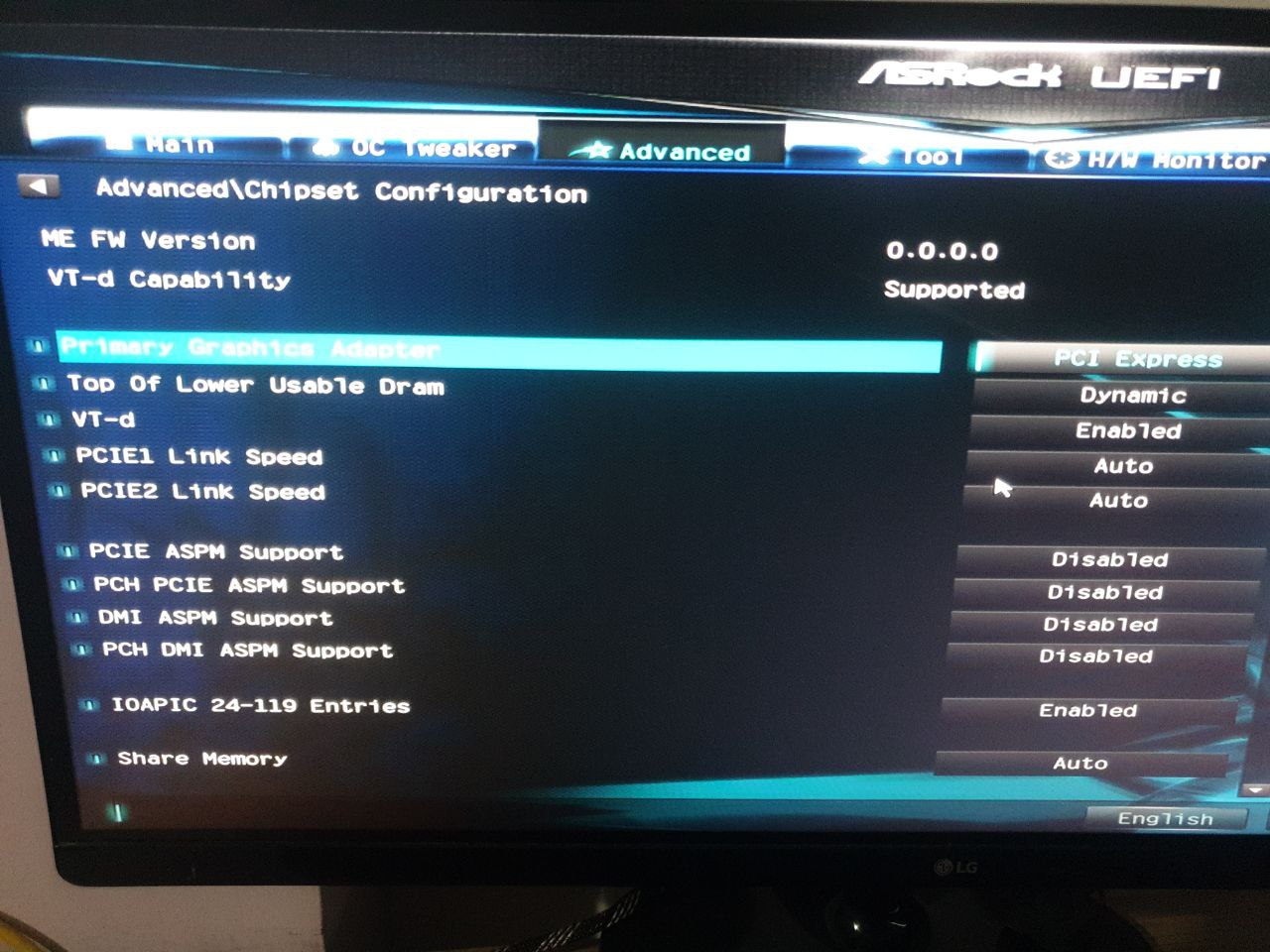

Currently working on trying coreboot on ASRock H110M-DVS rev 3.0

Coreboot from rev2.0 do not work on 3.0 !

I tried to flash directly working rom from 2.0 to 3.0 but did`t work !

Most likely some changes to coreboot need to be made for rev 3.0 to work!

Our telegram group for fast updates!

https://t.me/+h2K5CX5jEZA0MWJk

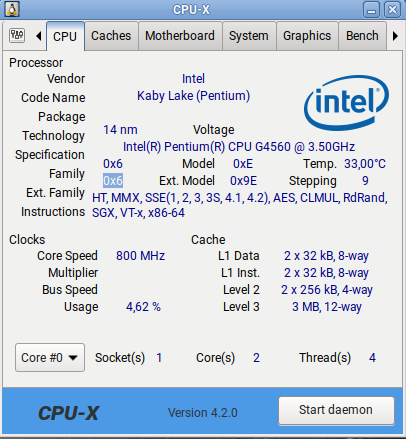

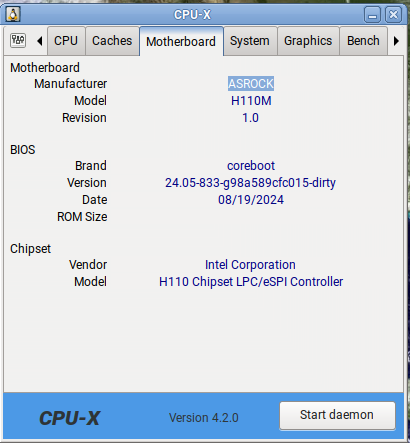

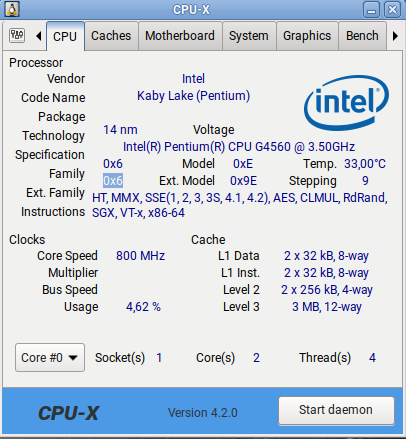

Current test cpu is:

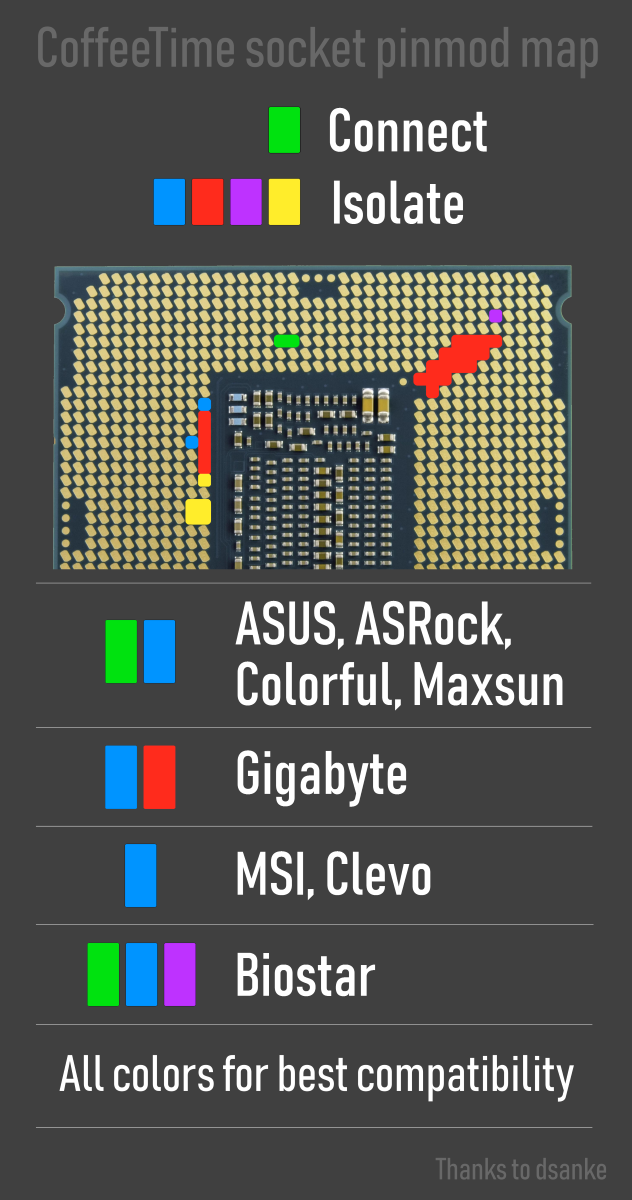

This mini-ITX board shall be able to support up to 9900k with some modification.

And this intel cc150 cpu has been made specifically for NVIDIA from intel.

(Board not support it stock! we need some additional modification to make it work)!

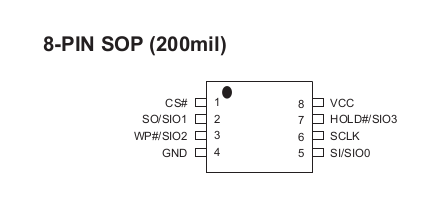

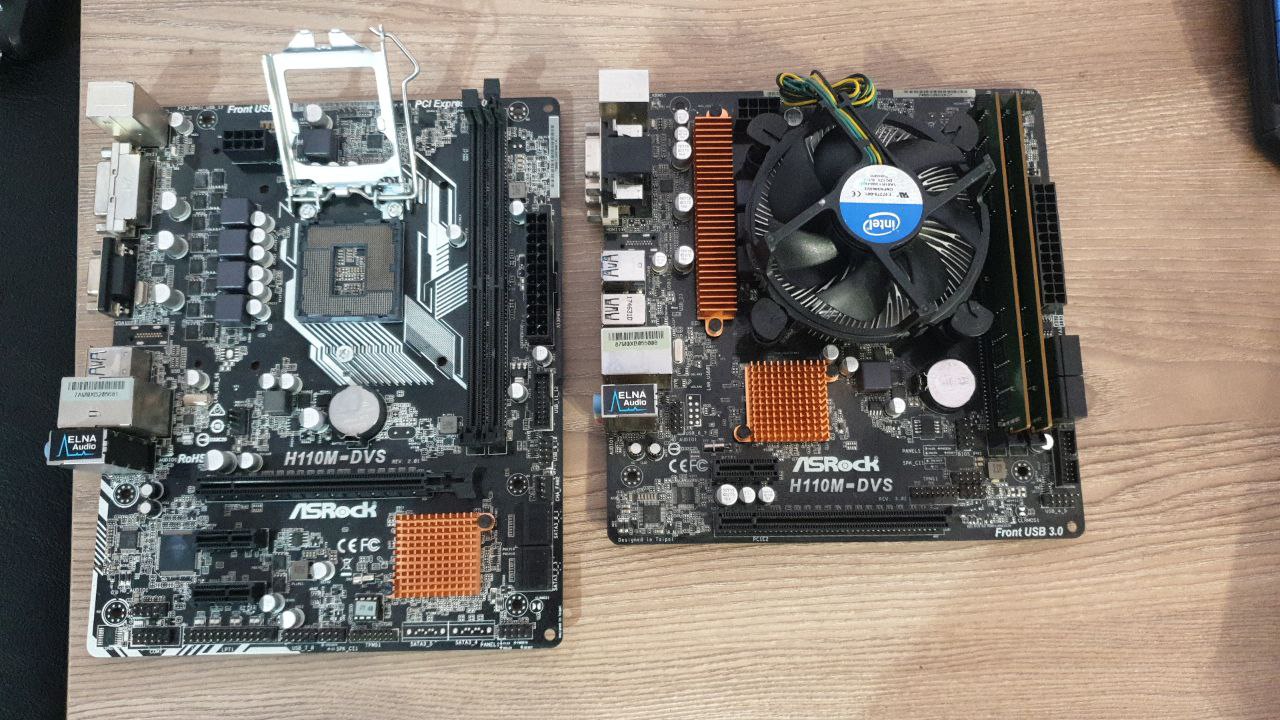

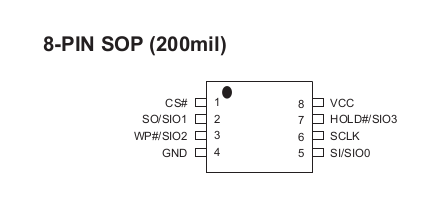

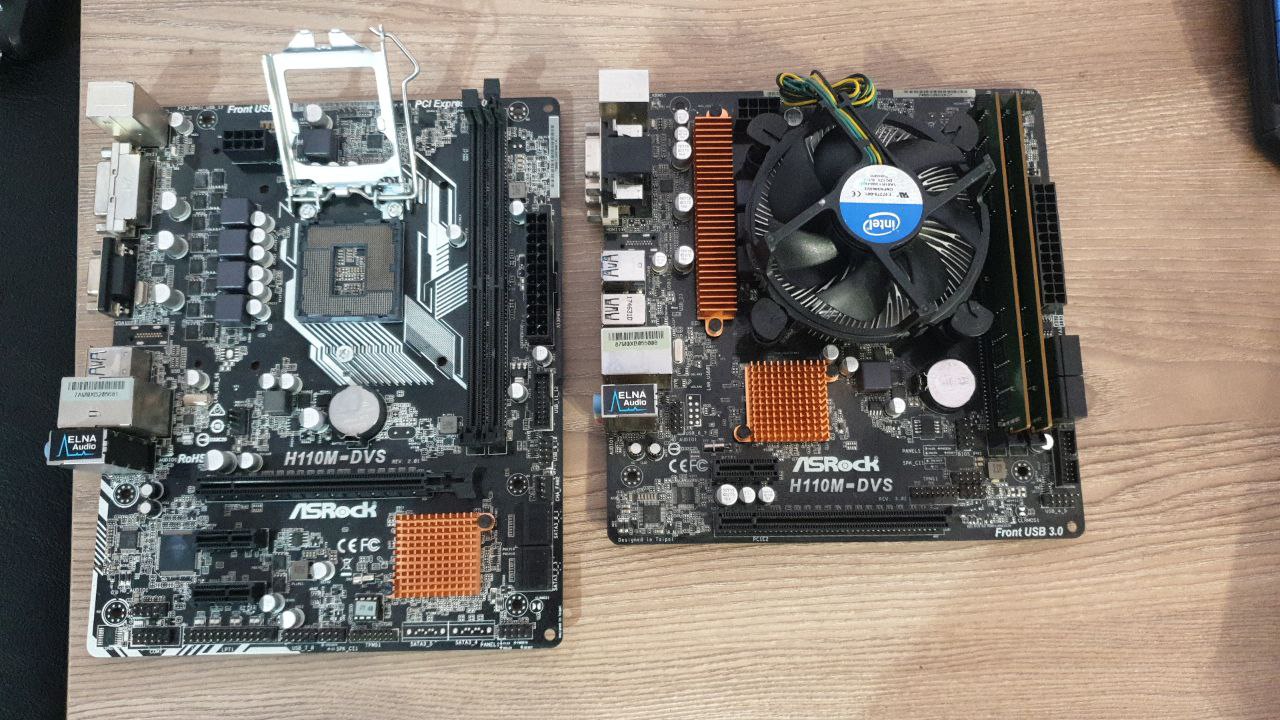

Rev 2.0

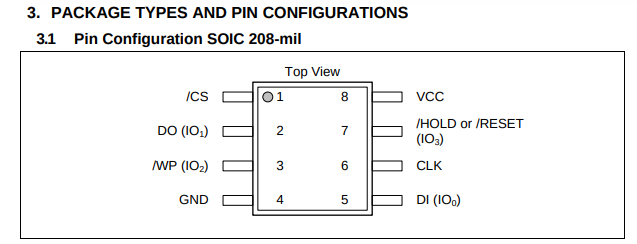

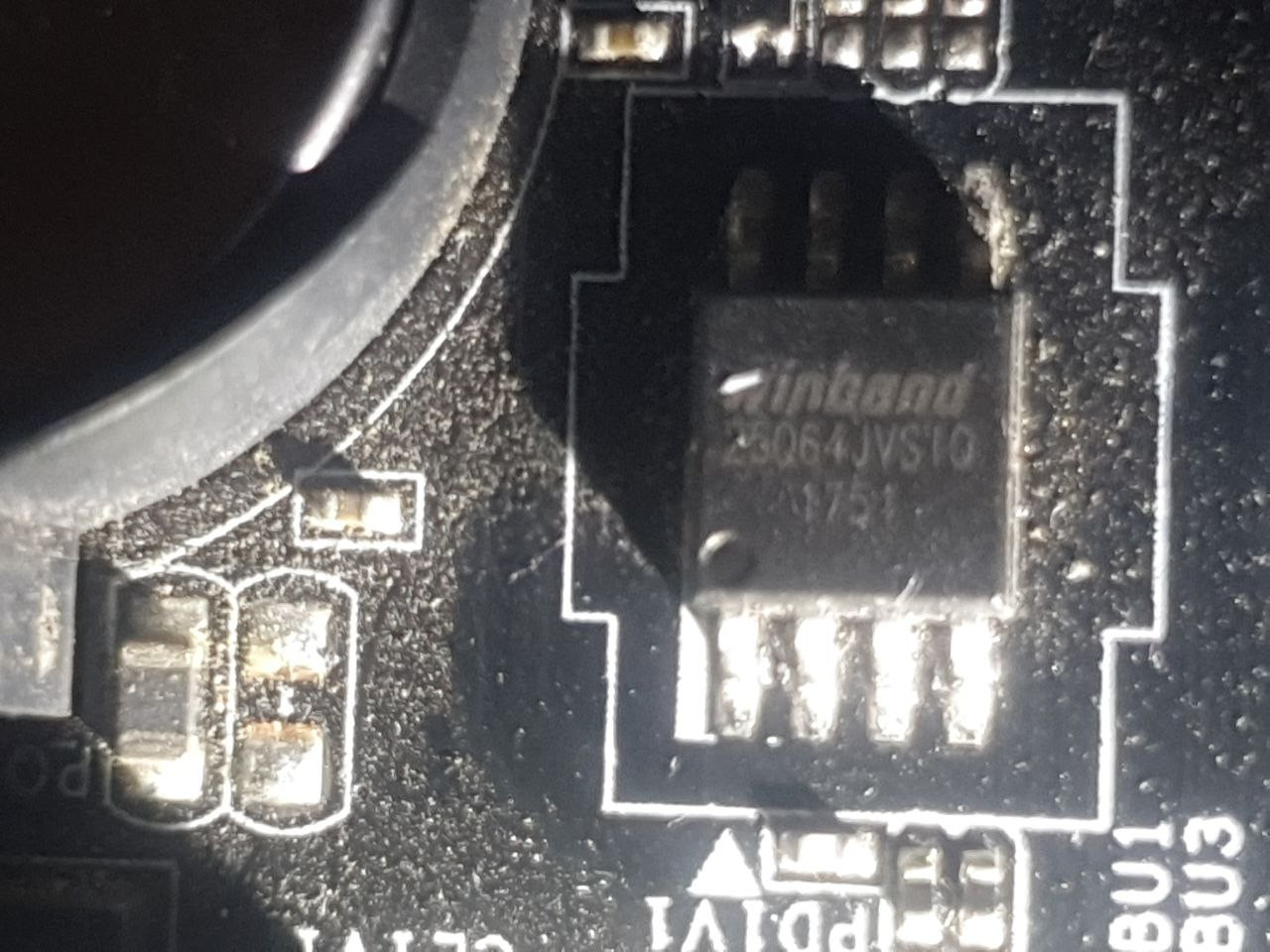

Rev 3.0

It seems the chip is MX25L6473E for rev 2.0 and for revision 3.0 they use "W25Q64JV-.Q"

PDF:

https://www.iot-tech.dev/fimg/MX25L6475E.PDF

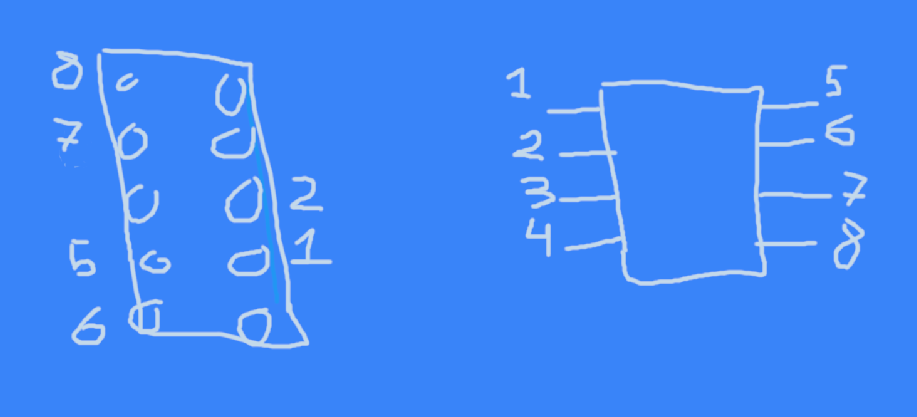

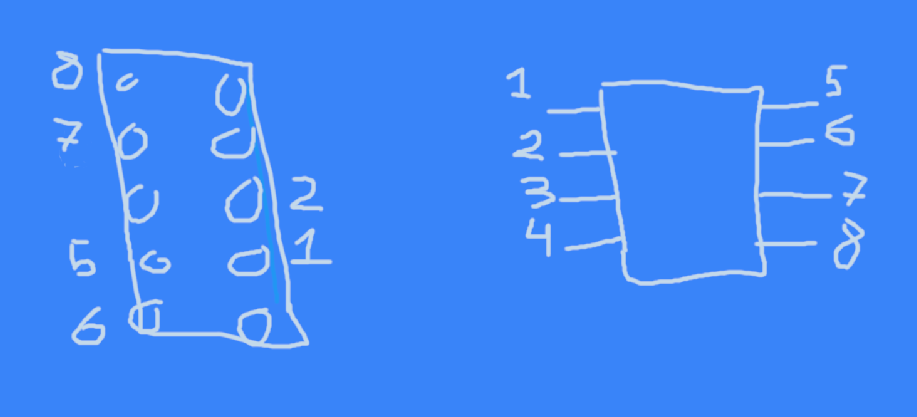

MX25L6473E Pinout (for an 8-pin SOP or WSON package):

Pin 1 (CS#): Chip Select (Active Low)

Pin 2 (SO): Serial Data Output (MISO)

Pin 3 (WP#): Write Protect (can be tied to 3.3V if not used)

Pin 4 (GND): Ground

Pin 5 (SI): Serial Data Input (MOSI)

Pin 6 (SCLK): Serial Clock

Pin 7 (HOLD#): Hold (can be tied to 3.3V if not used)

Pin 8 (VCC): Power Supply (3.3V)

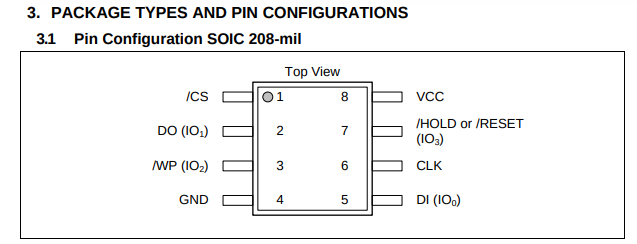

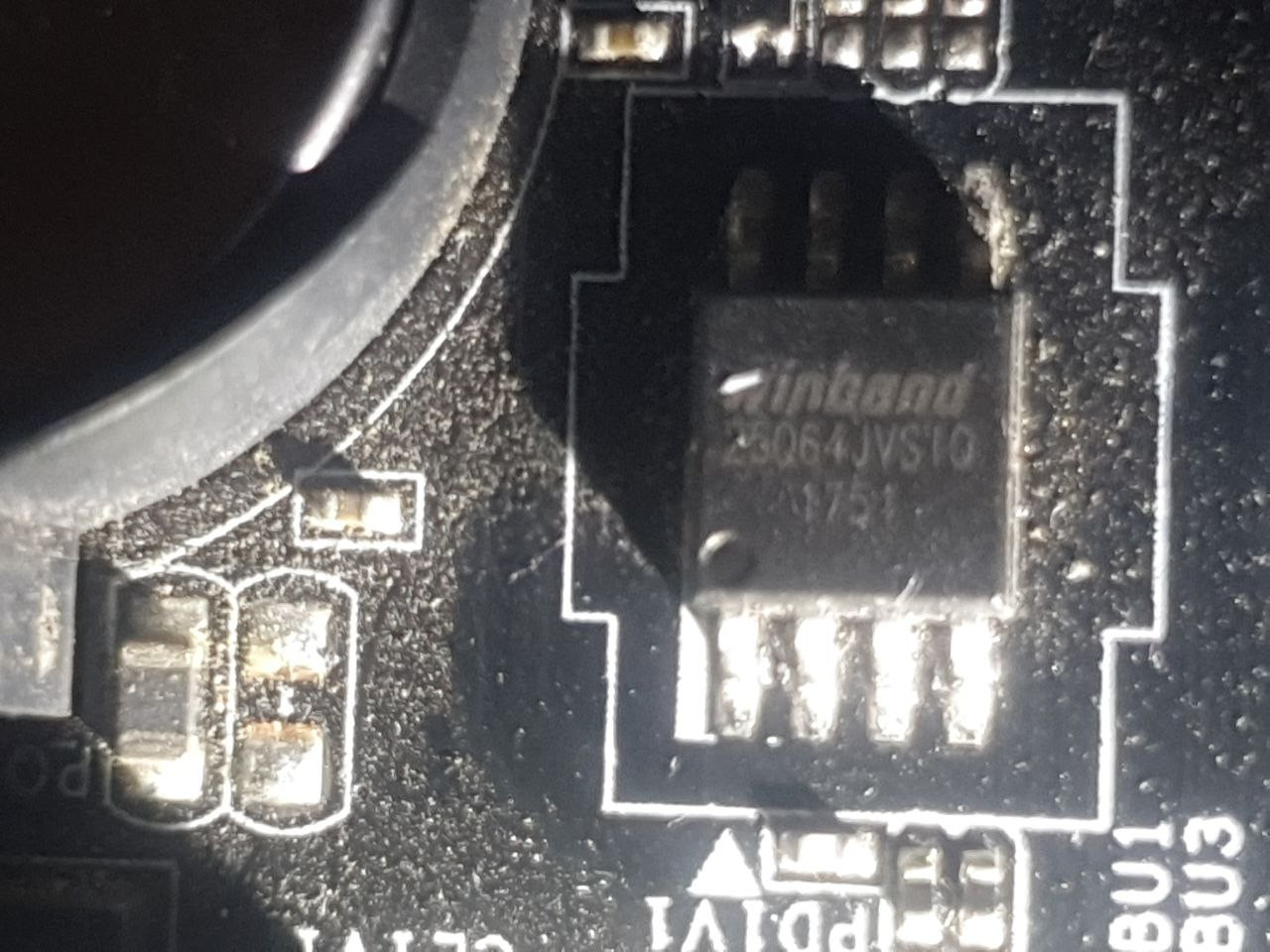

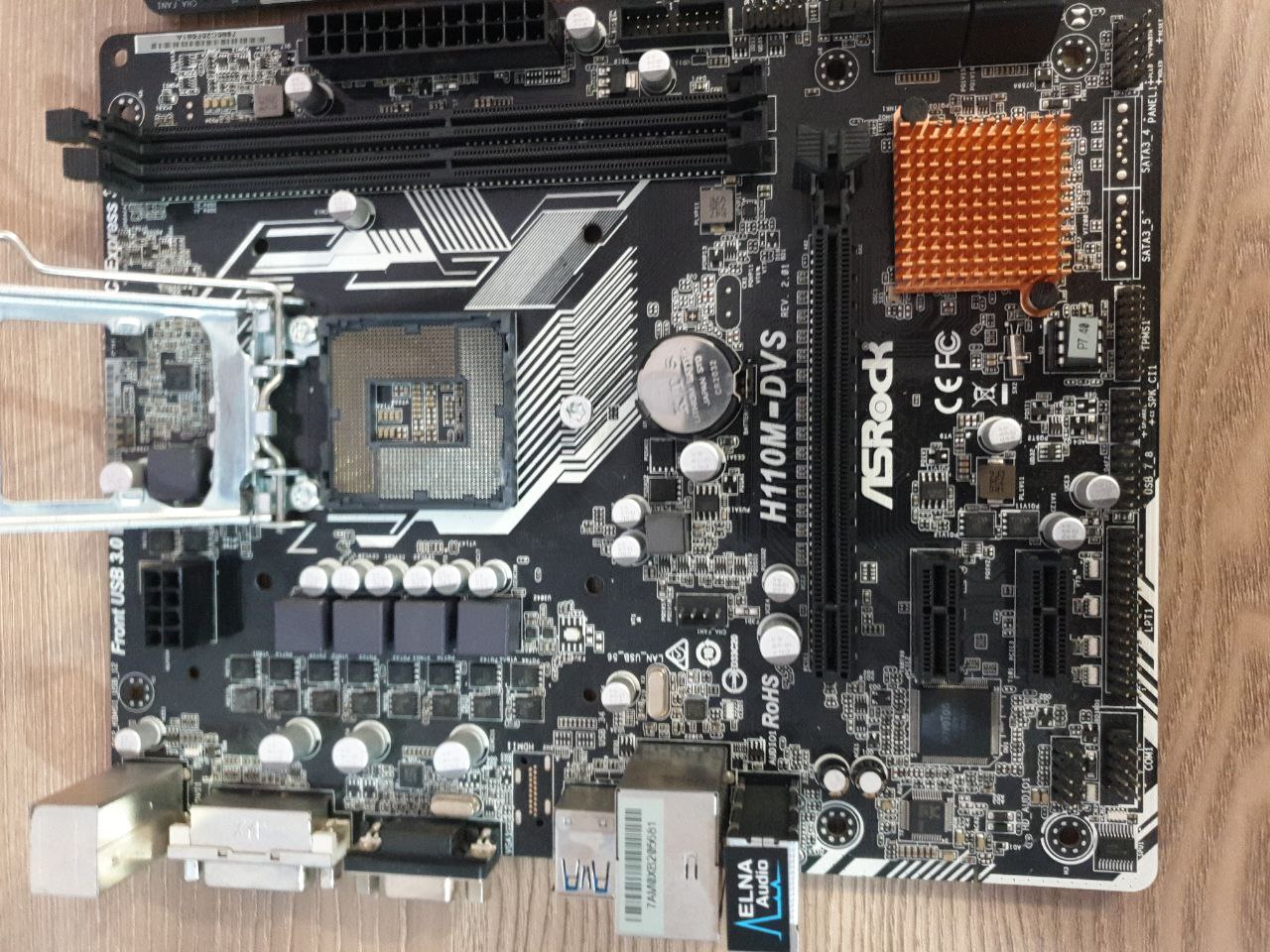

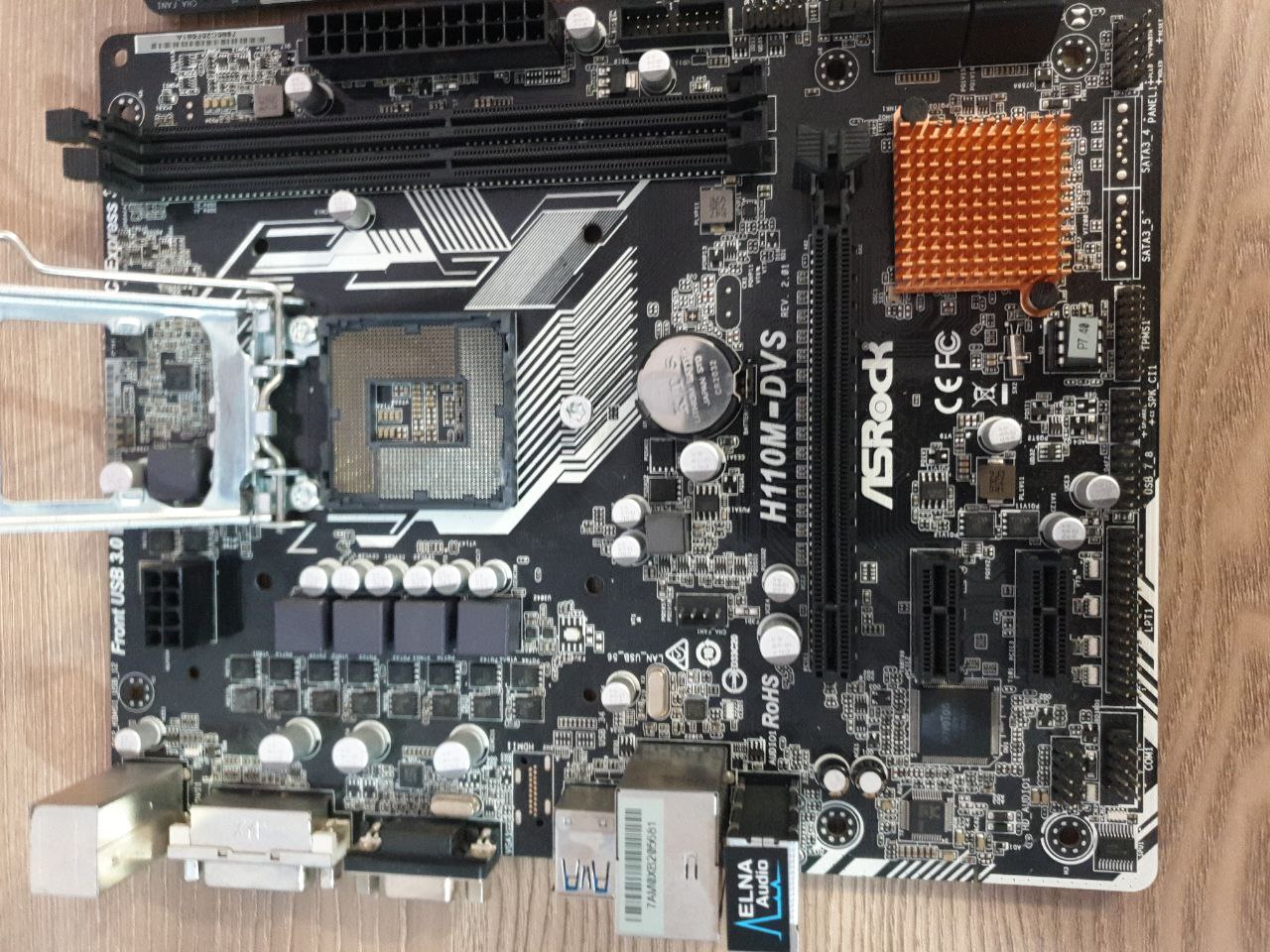

Here is for rev 3.0

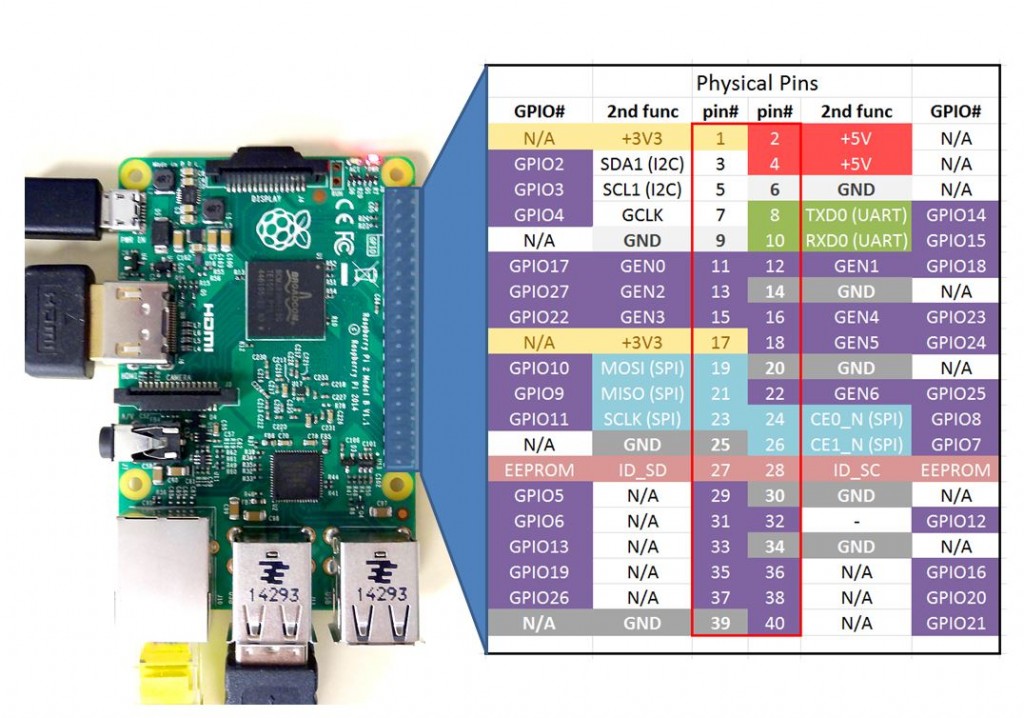

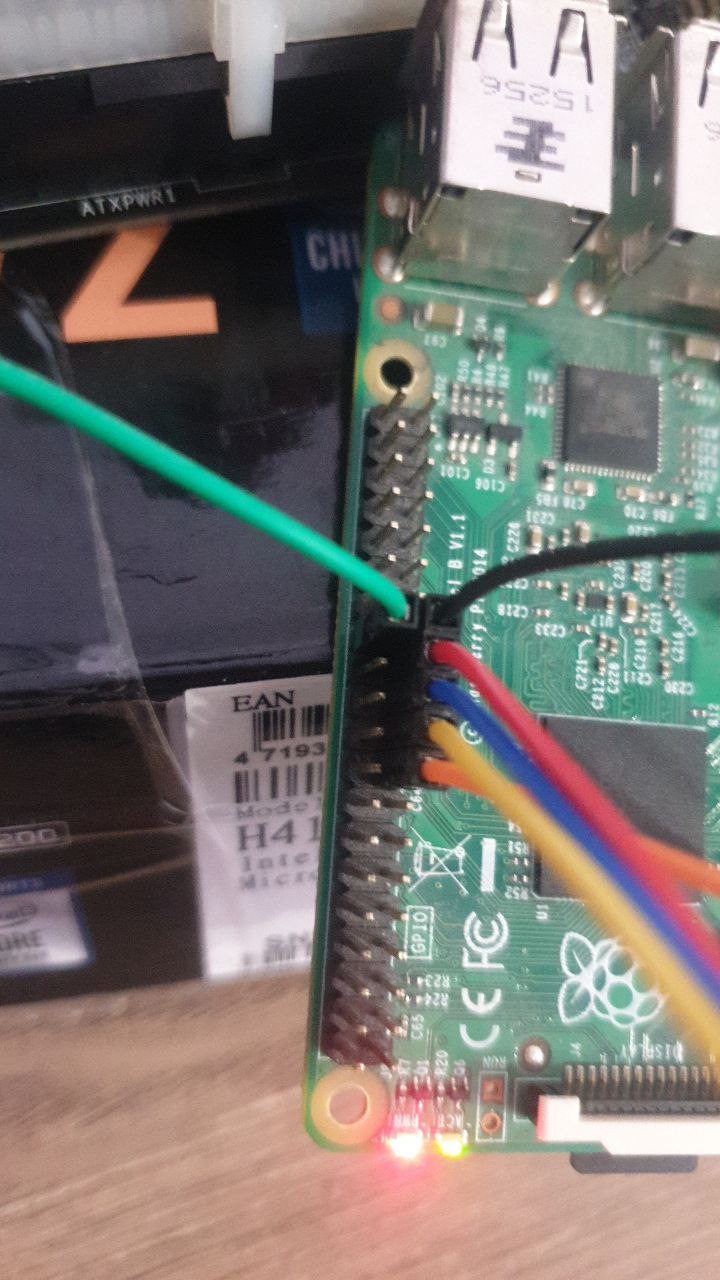

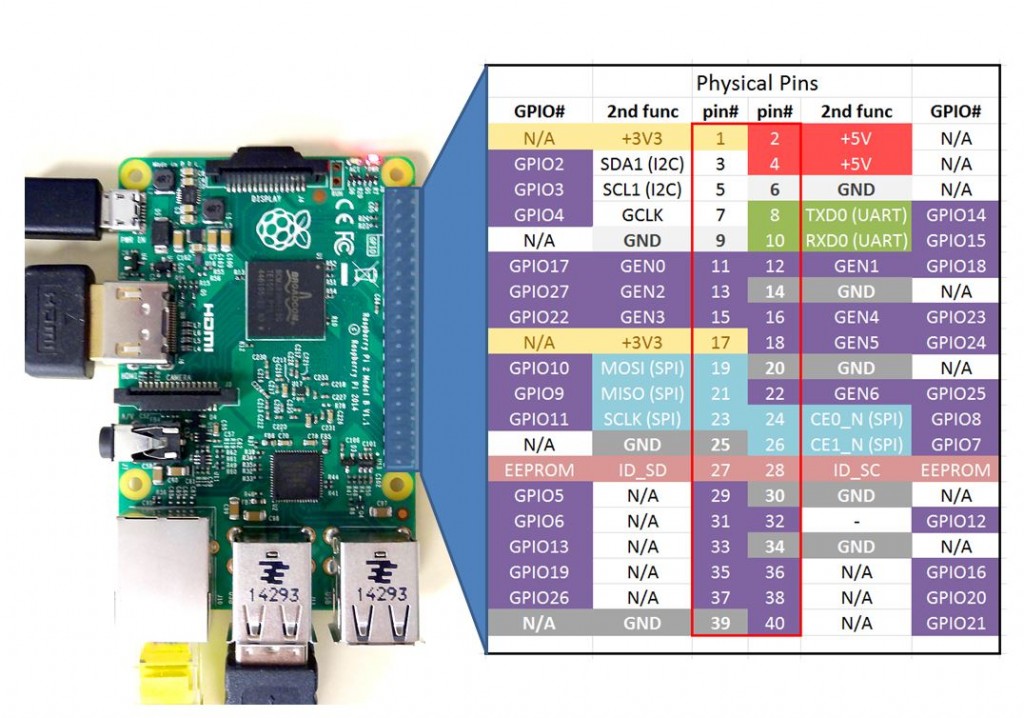

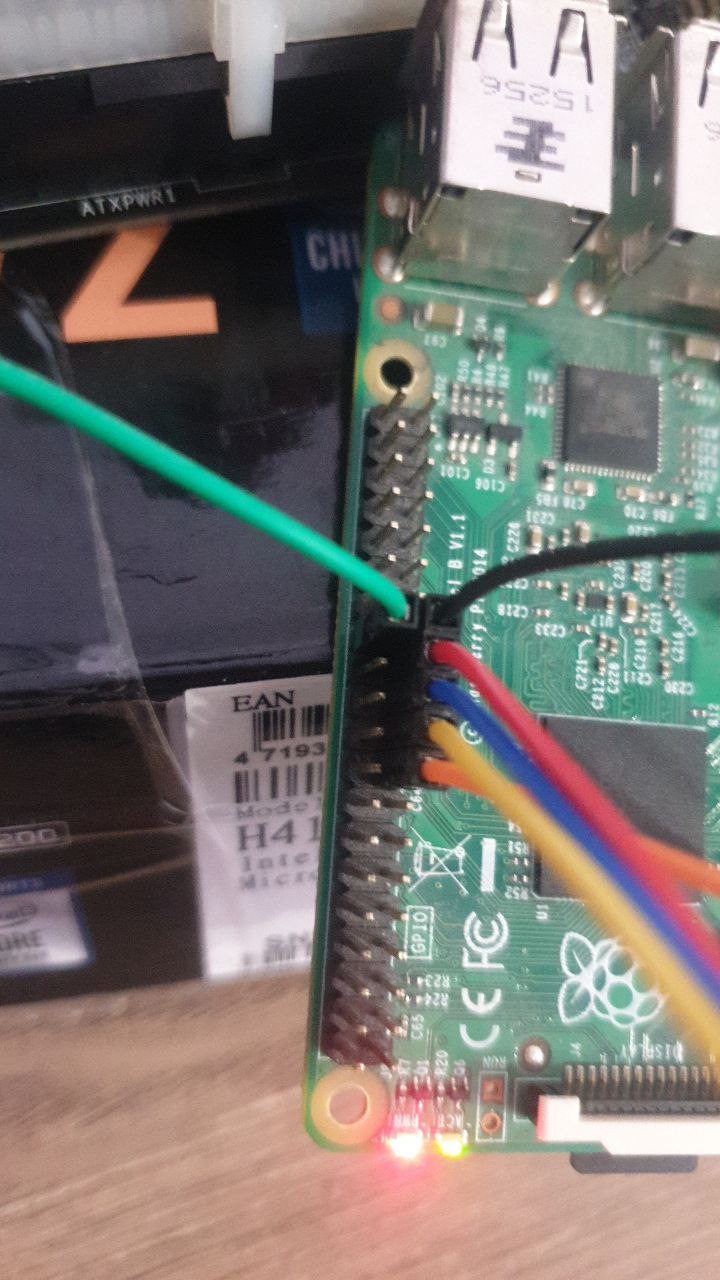

And here how i`m trying to connect it to Pi2 SPI bus for extracting original rom image with ME region!

Raspberry Pi 2 GPIO Pinout (SPI):

Pin 19 yellow (GPIO 10, MOSI): Connect to Pin 5 (SI) of the flash

Pin 21 blue (GPIO 9, MISO): Connect to Pin 2 (SO) of the flash.

Pin 23 red (GPIO 11, SCLK): Connect to Pin 6 (SCLK) of the flash.

Pin 24or26(spi0.0 or spi0.1) green: Connect to Pin 1 (CS#) of the flash.

Pin 25 black (GND): Connect to Pin 4 (GND) of the flash.

Pin 17 orange(3.3V): Connect to Pin 8 (VCC) of the flash.

Optional:

WP# and HOLD# Pins: Tie these to 3.3V (Pin 17) if you're not using them.

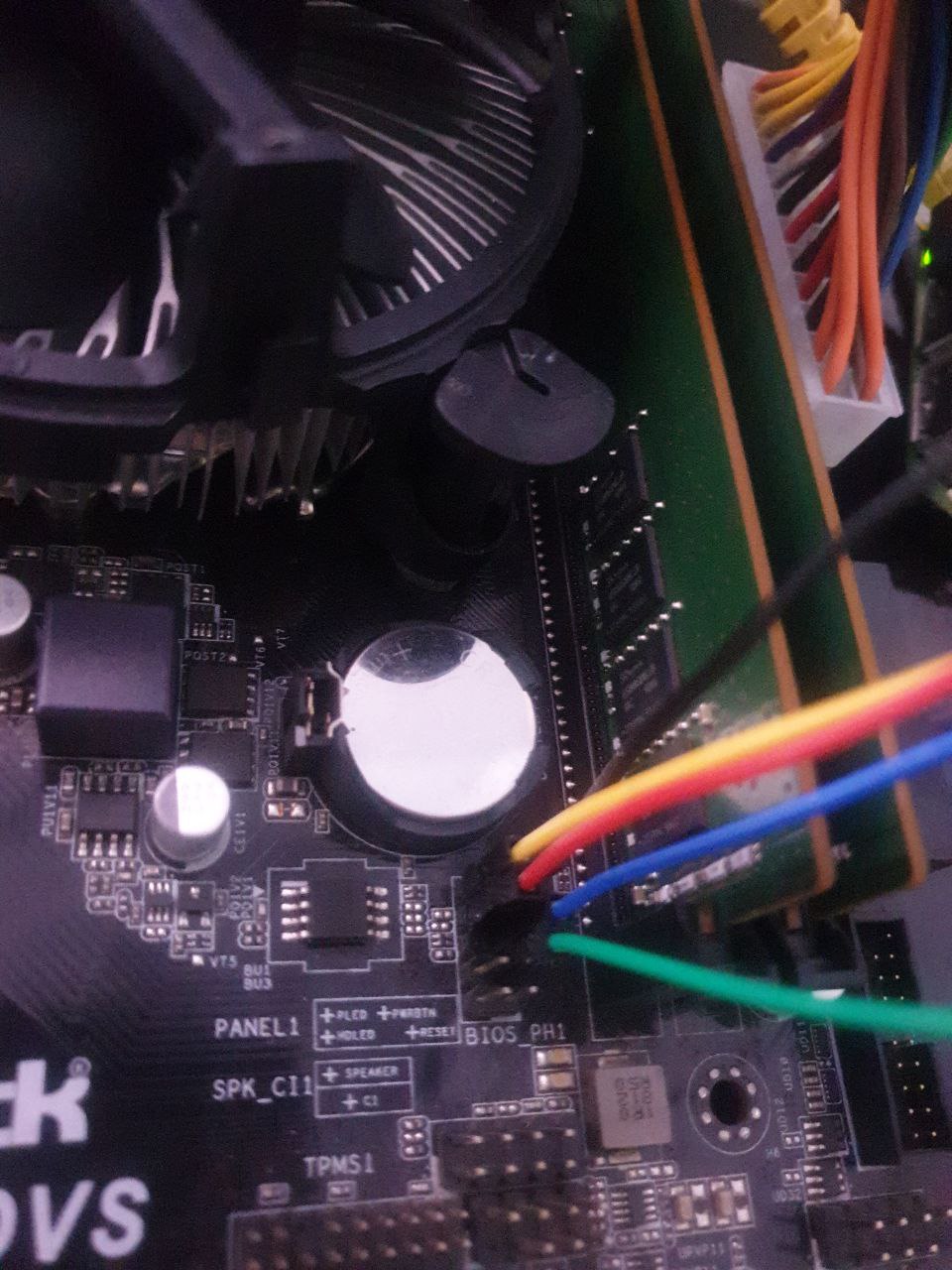

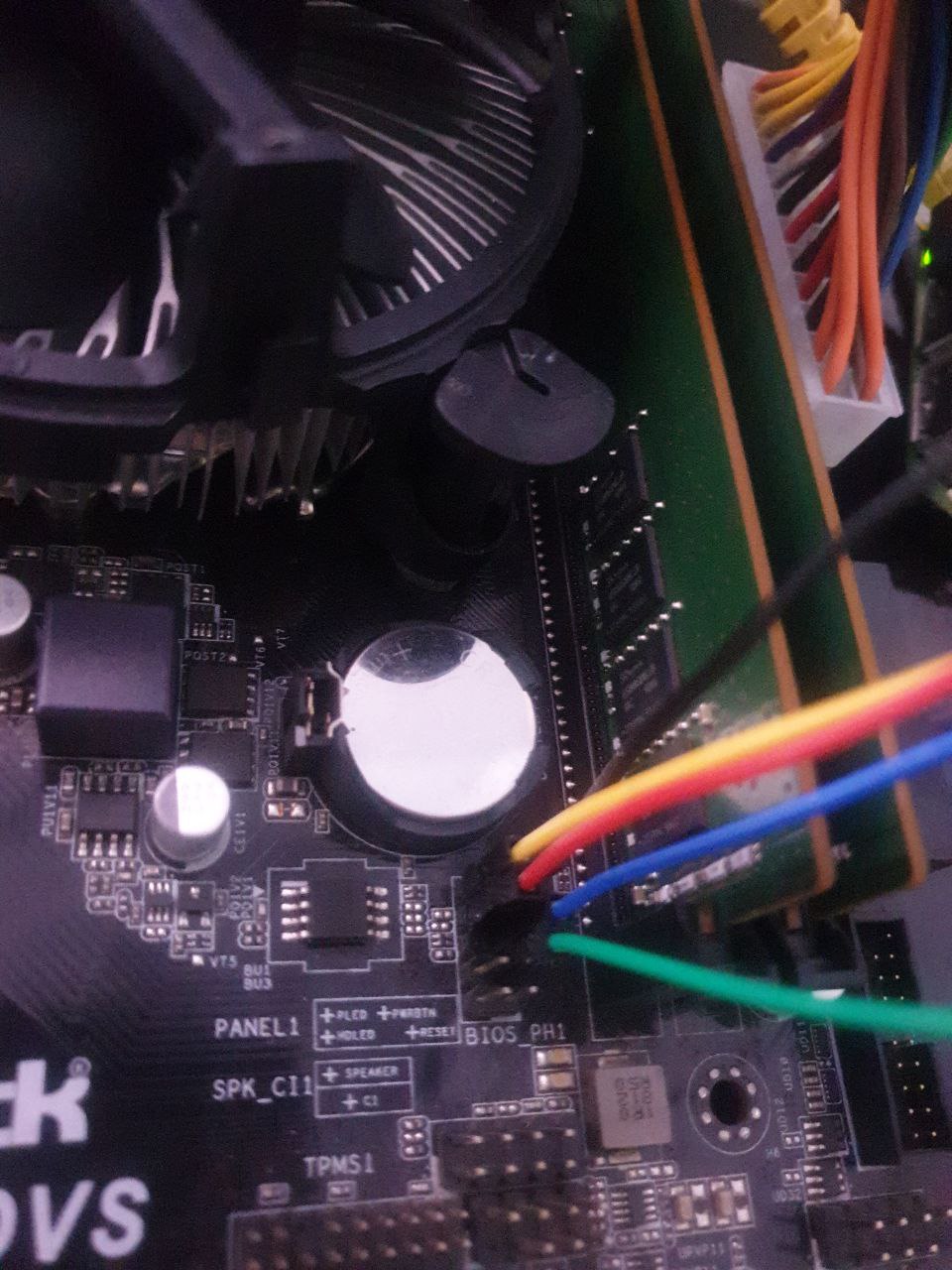

This mainboard has SPI pins out so quick after some digging here is the pin out: (i`m bad painter

(i`m bad painter  )

)

Reading the firmware is not easy task !

Even you wire everything correctly flashrom will not read it will tell you no flash chip is been found ...

Let me tell you how i did it !

1.Wire everything according to the diagram but do not connect vcc initially, remove the CMOS battery and power off the PSU (power supply)

2.Now connect the vcc pin to raspberry pi for like 5 sec and remove it !

3.Run the read command

Flashrom now will show you that is reading the firmware but when you open the rom file will be empty ! And yes if you connect 3.3V to vcc read will not happend !

So then you will ask how i did it ? Ok here is the solution after you reconnect vcc 3.3V for 5 sec you execute the command and same time turn power on

on the PSU switch then some glitch happening and chip magically unlock for reading and writing !

You can test by yourself that was the only way how we can dump the rom with no desoldering the chip !

Here is original bios from rev 3.0 dump!

https://www.iot-tech.dev/ff/ar/org.rom

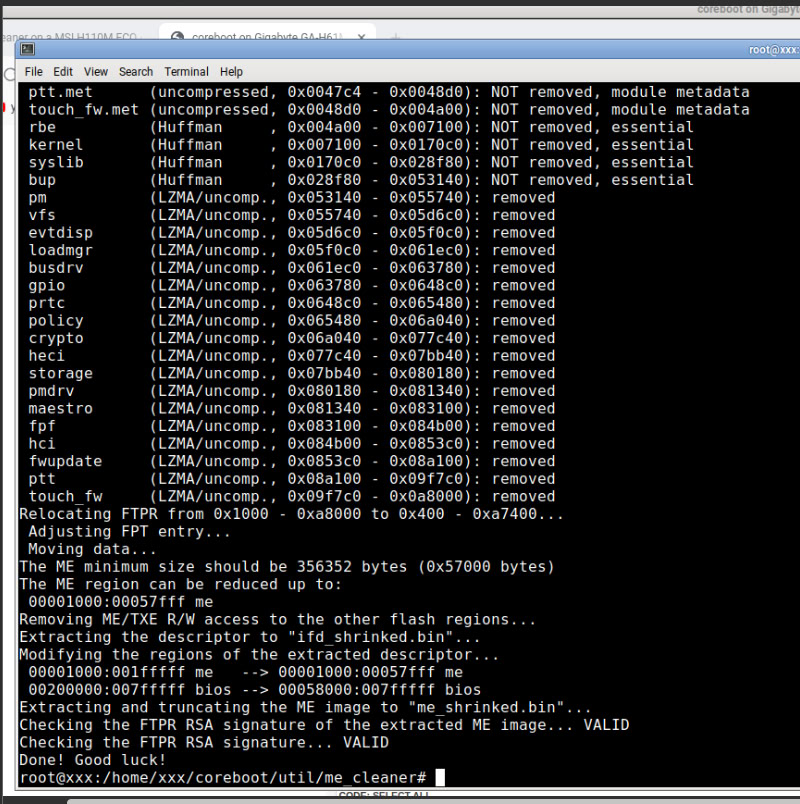

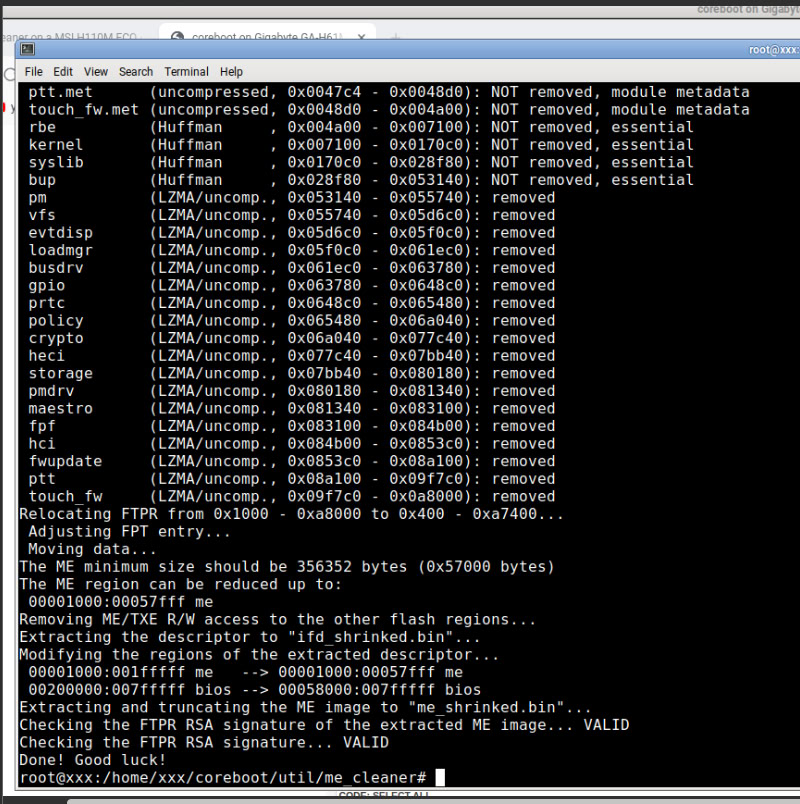

Now let remove the ME!

Here is ifd and cleaned me:

https://www.iot-tech.dev/ff/ar/ifd_shrinked.bin

https://www.iot-tech.dev/ff/ar/me_shrinked.bin

Here is Me clean stock original rom!

https://www.iot-tech.dev/ff/ar/mecleanout.bin

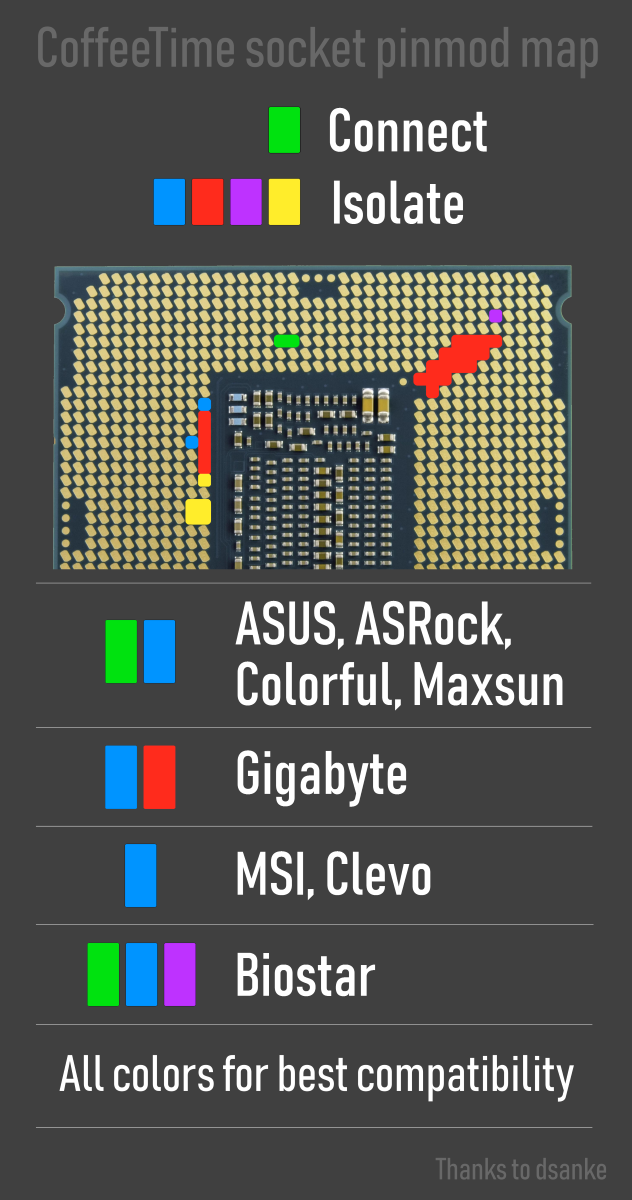

Here is Me clean KOFFELAKE PATCHED original rom!

https://www.iot-tech.dev/ff/ar/coffelakepatched.bin

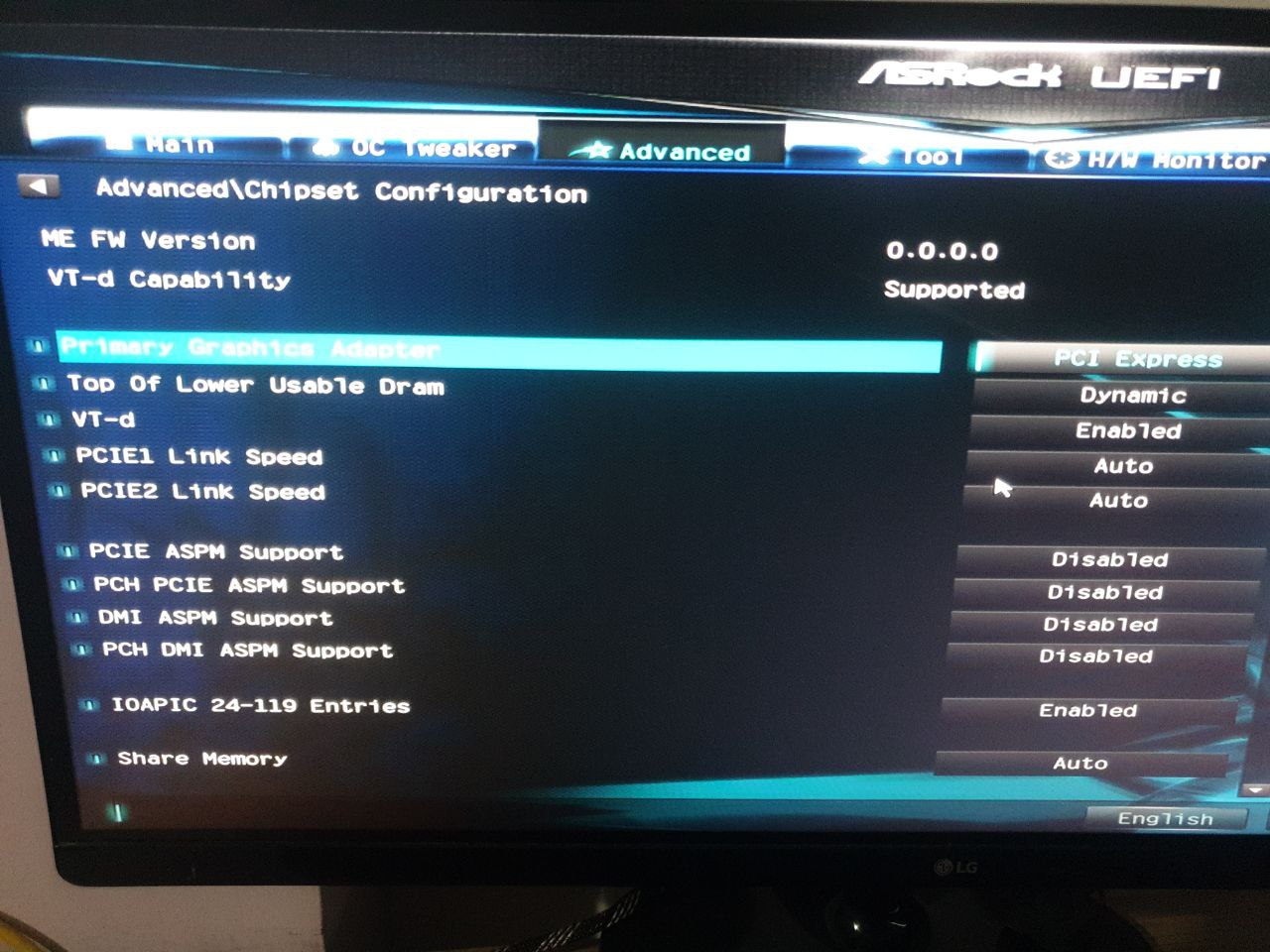

We can flash it and test it now! yep is working ME is gone from pci devices!

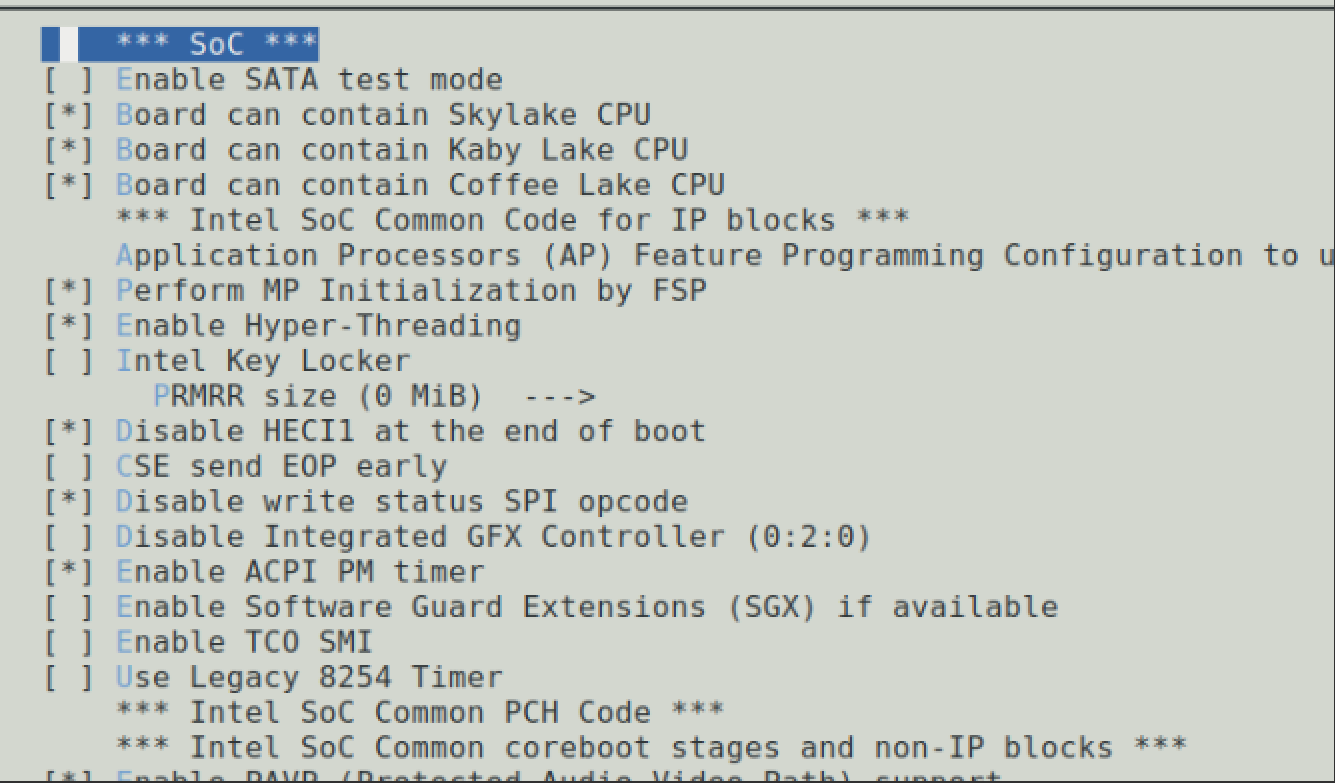

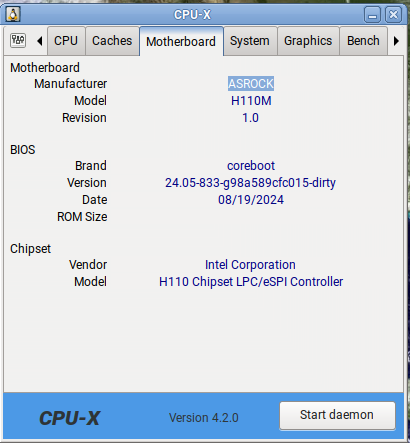

Let Build coreboot now !

Update 2:

Rev 2.0 arrived

Dumping the original rom with Pi2

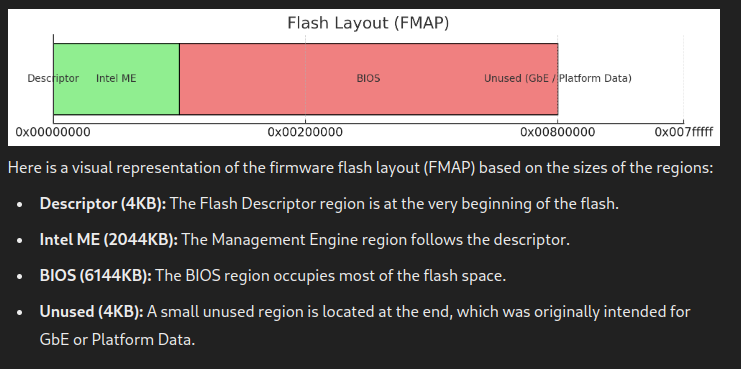

Ok after dumping the bios let see what is inside:

https://www.iot-tech.dev/ff/ar/asrockr2.0.rom

This will extract :

1 - ifd partition (it give info for all regions on the flash)

FLREG0: 0x00000000

Flash Region 0 (Flash Descriptor): 00000000 - 00000fff

Size: 0x00001000 (4KB) --> extracted file --> flashregion_0_flashdescriptor.bin

Download: https://www.iot-tech.dev/ff/ar/flashreg ... riptor.bin

===============================================================

2 - BIOS Region (FLREG1): (bios of the mainboard)

FLREG1: 0x07ff0200

Flash Region 1 (BIOS): 00200000 - 007fffff --> extracted file --> flashregion_1_bios.bin

Size: 0x00600000 (6MB)

===============================================================

3 - Intel ME Region (FLREG2): (intel ME firmware)

FLREG2: 0x01ff0001

Flash Region 2 (Intel ME): 00001000 - 001fffff --> extracted file -->flashregion_2_intel_me.bin

Size: 0x001ff000 (almost 2MB)

Download: https://www.iot-tech.dev/ff/ar/flashreg ... tel_me.bin

Me-Neutralized: https://www.iot-tech.dev/ff/ar/mec.bin

===============================================================

4 - GbE Region (FLREG3): (Unused)

FLREG3: 0x00007fff

Flash Region 3 (GbE): 00fff000 - 00000fff (unused)

===============================================================

5 - Platform Data Region (FLREG4): (Unused)

FLREG4: 0x00007fff

Flash Region 4 (Platform Data): 00fff000 - 00000fff (unused)

Let Build coreboot for Rev 2.0 most likely will work with 3.0 but need to be tested !

To build coreboot we need to set correct Fmap and CBFS size in our case is 0x00600000

Fmap is set by default for this mainboard based on original rom and we need to only add CBFS!

Then we need to add intel descriptor and me firmware !

Note!

If you provide different ifd descriptor than what is on original rom coreboot will build but it will not boot most likely modification of FMAP on coreboot will be needed.

Example:

let say you want to change ifd to make the size of coreboot bios bigger aka CBFS.

Coreboot builds successfully ! i used seabios and EDK2 as payload PS2 keyboard works on both usb not working on sea bios but is working on EDK2.

To download this coreboot rom visit our telegram group !

Our telegram group for fast updates!

https://t.me/+h2K5CX5jEZA0MWJk

======================================================================================================

Resources:

https://github.com/corna/me_cleaner

https://chromium.googlesource.com/chrom ... 10m-dvs.md

https://doc.coreboot.org/mainboard/asro ... m-dvs.html

https://github.com/corna/me_cleaner/wik ... -H110M-ECO

youtu.be/W7nYV8QwwRg

youtu.be/CZADlI-Hge8

Coreboot from rev2.0 do not work on 3.0 !

I tried to flash directly working rom from 2.0 to 3.0 but did`t work !

Most likely some changes to coreboot need to be made for rev 3.0 to work!

Our telegram group for fast updates!

https://t.me/+h2K5CX5jEZA0MWJk

Current test cpu is:

This mini-ITX board shall be able to support up to 9900k with some modification.

And this intel cc150 cpu has been made specifically for NVIDIA from intel.

(Board not support it stock! we need some additional modification to make it work)!

Rev 2.0

Rev 3.0

It seems the chip is MX25L6473E for rev 2.0 and for revision 3.0 they use "W25Q64JV-.Q"

PDF:

https://www.iot-tech.dev/fimg/MX25L6475E.PDF

MX25L6473E Pinout (for an 8-pin SOP or WSON package):

Pin 1 (CS#): Chip Select (Active Low)

Pin 2 (SO): Serial Data Output (MISO)

Pin 3 (WP#): Write Protect (can be tied to 3.3V if not used)

Pin 4 (GND): Ground

Pin 5 (SI): Serial Data Input (MOSI)

Pin 6 (SCLK): Serial Clock

Pin 7 (HOLD#): Hold (can be tied to 3.3V if not used)

Pin 8 (VCC): Power Supply (3.3V)

Here is for rev 3.0

And here how i`m trying to connect it to Pi2 SPI bus for extracting original rom image with ME region!

Raspberry Pi 2 GPIO Pinout (SPI):

Pin 19 yellow (GPIO 10, MOSI): Connect to Pin 5 (SI) of the flash

Pin 21 blue (GPIO 9, MISO): Connect to Pin 2 (SO) of the flash.

Pin 23 red (GPIO 11, SCLK): Connect to Pin 6 (SCLK) of the flash.

Pin 24or26(spi0.0 or spi0.1) green: Connect to Pin 1 (CS#) of the flash.

Pin 25 black (GND): Connect to Pin 4 (GND) of the flash.

Pin 17 orange(3.3V): Connect to Pin 8 (VCC) of the flash.

Optional:

WP# and HOLD# Pins: Tie these to 3.3V (Pin 17) if you're not using them.

This mainboard has SPI pins out so quick after some digging here is the pin out:

Reading the firmware is not easy task !

Even you wire everything correctly flashrom will not read it will tell you no flash chip is been found ...

Let me tell you how i did it !

1.Wire everything according to the diagram but do not connect vcc initially, remove the CMOS battery and power off the PSU (power supply)

2.Now connect the vcc pin to raspberry pi for like 5 sec and remove it !

3.Run the read command

Code: Select all

flashrom -p linux_spi:dev=/dev/spidev0.1,spispeed=8000 -c "W25Q64JV-.Q" -r original.rom

So then you will ask how i did it ? Ok here is the solution after you reconnect vcc 3.3V for 5 sec you execute the command and same time turn power on

on the PSU switch then some glitch happening and chip magically unlock for reading and writing !

You can test by yourself that was the only way how we can dump the rom with no desoldering the chip !

Here is original bios from rev 3.0 dump!

https://www.iot-tech.dev/ff/ar/org.rom

Now let remove the ME!

Code: Select all

python me_cleaner.py -r -t -d -O mecleanout.bin -D ifd_shrinked.bin -M me_shrinked.bin /home/user/org.rom

Here is ifd and cleaned me:

https://www.iot-tech.dev/ff/ar/ifd_shrinked.bin

https://www.iot-tech.dev/ff/ar/me_shrinked.bin

Here is Me clean stock original rom!

https://www.iot-tech.dev/ff/ar/mecleanout.bin

Here is Me clean KOFFELAKE PATCHED original rom!

https://www.iot-tech.dev/ff/ar/coffelakepatched.bin

We can flash it and test it now! yep is working ME is gone from pci devices!

Code: Select all

flashrom -p linux_spi:dev=/dev/spidev0.1,spispeed=8000 -c "W25Q64JV-.Q" -w mecleanout.bin

Let Build coreboot now !

Update 2:

Rev 2.0 arrived

Dumping the original rom with Pi2

Ok after dumping the bios let see what is inside:

https://www.iot-tech.dev/ff/ar/asrockr2.0.rom

Code: Select all

ifdtool -x original_bios.bin

ifdtool -d flashregion_0_flashdescriptor.bin

This will extract :

1 - ifd partition (it give info for all regions on the flash)

FLREG0: 0x00000000

Flash Region 0 (Flash Descriptor): 00000000 - 00000fff

Size: 0x00001000 (4KB) --> extracted file --> flashregion_0_flashdescriptor.bin

Download: https://www.iot-tech.dev/ff/ar/flashreg ... riptor.bin

===============================================================

2 - BIOS Region (FLREG1): (bios of the mainboard)

FLREG1: 0x07ff0200

Flash Region 1 (BIOS): 00200000 - 007fffff --> extracted file --> flashregion_1_bios.bin

Size: 0x00600000 (6MB)

===============================================================

3 - Intel ME Region (FLREG2): (intel ME firmware)

FLREG2: 0x01ff0001

Flash Region 2 (Intel ME): 00001000 - 001fffff --> extracted file -->flashregion_2_intel_me.bin

Size: 0x001ff000 (almost 2MB)

Download: https://www.iot-tech.dev/ff/ar/flashreg ... tel_me.bin

Me-Neutralized: https://www.iot-tech.dev/ff/ar/mec.bin

===============================================================

4 - GbE Region (FLREG3): (Unused)

FLREG3: 0x00007fff

Flash Region 3 (GbE): 00fff000 - 00000fff (unused)

===============================================================

5 - Platform Data Region (FLREG4): (Unused)

FLREG4: 0x00007fff

Flash Region 4 (Platform Data): 00fff000 - 00000fff (unused)

Let Build coreboot for Rev 2.0 most likely will work with 3.0 but need to be tested !

To build coreboot we need to set correct Fmap and CBFS size in our case is 0x00600000

Fmap is set by default for this mainboard based on original rom and we need to only add CBFS!

Then we need to add intel descriptor and me firmware !

Note!

If you provide different ifd descriptor than what is on original rom coreboot will build but it will not boot most likely modification of FMAP on coreboot will be needed.

Example:

let say you want to change ifd to make the size of coreboot bios bigger aka CBFS.

Coreboot builds successfully ! i used seabios and EDK2 as payload PS2 keyboard works on both usb not working on sea bios but is working on EDK2.

To download this coreboot rom visit our telegram group !

Our telegram group for fast updates!

https://t.me/+h2K5CX5jEZA0MWJk

======================================================================================================

Resources:

https://github.com/corna/me_cleaner

https://chromium.googlesource.com/chrom ... 10m-dvs.md

https://doc.coreboot.org/mainboard/asro ... m-dvs.html

https://github.com/corna/me_cleaner/wik ... -H110M-ECO

youtu.be/W7nYV8QwwRg

youtu.be/CZADlI-Hge8